# IMPROVING COMMUNICATION PERFORMANCE IN GPU-ACCELERATED HPC CLUSTERS

by

### Iman Faraji

A thesis submitted to the Department of Electrical and Computer Engineering in conformity with the requirements for the degree of Doctor of Philosophy

Queen's University

Kingston, Ontario, Canada

January 2018

Copyright © Iman Faraji, 2018

### Abstract

In recent years, GPUs have been adopted in many High-Performance Computing (HPC) clusters due to their massive computational power and energy efficiency. The Message Passing Interface (MPI) is the de-facto standard for parallel programming. Many HPC applications, written in MPI, use parallel processes and multiple GPUs to achieve higher performance and GPU memory capacity. In such applications, efficiently performing GPU inter-process communication is the key in the application performance.

In this dissertation, we present proposals to improve the GPU inter-process communication in HPC clusters using novel GPU-aware designs, efficient and scalable algorithms, topology-aware designs, and hardware features. Specifically, we propose various approaches to improve the efficiency of MPI communication routines in GPU clusters. We also propose designs that evaluate the total application inter-process communication and provide solutions to improve its efficiency.

First, we propose efficient GPU-aware algorithms to improve MPI collective performance. We show the importance of minimizing CPU intervention on GPU collective performance. We also utilize GPU features to enhance both collective communication and computation.

As inter-process communications scale to across multi-GPU nodes and clusters,

efficient inter-process communication routines must consider the physical structure of the underlying system. Given the hierarchical nature of the GPU clusters with multi-GPU nodes, we propose hierarchy-aware designs for GPU collectives and show that different algorithms are favored at different hierarchy levels.

With the presence of multiple data copy mechanisms in modern GPU clusters, it is crucial to make an informed decision on how to use them for efficient inter-process communications. In this regard, we propose designs that intelligently decide which data copy mechanisms to use in GPU collectives. Using these designs, we reveal the importance of using multiple data copy mechanisms in performing multiple interprocess communications.

Finally, we provide topology-aware solutions to improve the application interprocess communication efficiency, both within multi-GPU nodes and across GPU clusters. First, we study the performance of different communication channels used for GPU inter-process communications. Next, we propose topology-aware designs that consider both the system physical topology and application communication pattern. These designs improve the communication performance by performing more intensive inter-process communication on stronger communication channels.

### Statement of Collaboration

The work in Chapter 6 was conducted collaboratively with Dr. Hessam Mirsadeghi. The proposed design in Section 6.3.1 on topology-aware GPU selection schemes on a multi-GPU node was mainly proposed and developed by me, and Dr. Mirsadeghi provided some technical support and insights. The proposed work in Section 6.3.2 on a 3-phase mapping approach for GPU clusters was mainly proposed and developed by Dr. Mirsadeghi; I provided technical and intellectual assistance, and took care of designing and integrating the third phase of the design.

Microbenchmarks were developed jointly. Dr. Mirsadeghi specifically provided some technical supports regarding the implementation of different communication patterns that were used in our microbenchmarks. The extension of the microbenchmarks to support GPU devices was done by me. Moreover, I developed a microbenchmark suite for cluster-wide experiments; this benchmark is capable of providing simultaneous communications among CPUs and among GPUs with different communication patterns.

All the pre- and post-analysis results in this chapter were gathered by me. This includes gathering the motivational, profiling, microbenchmark, and application results. Analysis of the microbenchmark and application results were performed jointly, while analysis of the motivational and profiling results were mainly performed by me.

I also extended the FPMPI profiler to gather the HOOMD-Blue application profiling results.

## Acknowledgments

My deep gratitude first goes to my supervisor, Dr. Ahmad Afsahi, for his invaluable support and feedback in writing this dissertation. I am thankful for his intellectual support and expert guidance in my PhD research and study. I also thank him for the patience, focus, and enthusiasm that he has with research that was contagious and motivational for me, particularly during tough times of my PhD career. I would also like to thank the my thesis examining committee, Dr. Tom Dean, Dr. Patrick Martin , Dr. Steven Blostein, and Dr. Tarek Abdelrahman for their feedbacks and comments.

I would like to thank for the financial support provided by Natural Science and Engineering Research Council of Canada (NSERC), Queen's Graduate Award (QGA), and International Tuition Award (ITA) to conduct this research. I also thank Electrical and Computer Engineering Department for the teaching assistantship and fellowship awards. I would also like to acknowledge the resource support from Compute Canada, Calcul Quebec, and the HPC Advisory Council, and especially thank Maxime Boissonneault and Pak Lui for their technical support.

I am thankful to all my colleagues in Parallel Processing Research Laboratory, Dr. Mohammad Javad Rashti, Dr. Ryan Grant, Dr. Reza Zamani, Dr. Judicael Zounmevo, Dr. Hessam Mirsadeghi, Grigori Inozemtsev, Mahdieh Ghazimirsaeeed, Kaushal Kumar, Mac Fregeau, and Ramapriya Balasubramaniam for their support and great discussions during my PhD program. I am particularly thankful to Hessam Mirsadeghi for his collaboration in the topology-aware research and the technical assistance and intellectual support that he provided.

Finally, I would like to specially thank my family for all of their love, support, and encouragement. For my parents, Mitra and Saeed, who raised me with love and continuously and faithfully supported me in all of my pursuits. For my sister, Saharnaz and her caring support. I would also like to express my immense gratitude to my wife, Arghavan for her love, support, encouragement and patience. I am thankful for her invaluable presence during my PhD journey and look forward to embarking upon new journeys in life with her.

## Contents

| Abstra                      | $\operatorname{ct}$ |                                                   | i                |  |

|-----------------------------|---------------------|---------------------------------------------------|------------------|--|

| Statement of Collaboration  |                     |                                                   |                  |  |

| Ackno                       | Acknowledgments     |                                                   |                  |  |

| Table (                     | of Con              | tents                                             | vii              |  |

| List of                     | Table               | S                                                 | X                |  |

| List of                     | Figur               | es                                                | xi               |  |

| List of                     | Abbre               | eviation                                          | xv               |  |

| Chapte<br>1.1<br>1.2<br>1.3 | Proble<br>Contr     | Introduction em Statement                         | 1<br>4<br>5<br>8 |  |

| Chapte                      | er 2:               | Background                                        | 10               |  |

| 2.1                         | HPC                 | Clusters with Accelerators                        | 10               |  |

| 2.2                         | Graph               | nics Processing Units (GPUs)                      | 11               |  |

|                             | 2.2.1               | GPU Architectures                                 | 12               |  |

|                             | 2.2.2               | GPU Programming Languages and Tools               | 14               |  |

|                             | 2.2.3               | GPU Advanced Features                             | 19               |  |

| 2.3                         | Messa               | ge Passing Interface (MPI)                        | 21               |  |

|                             | 2.3.1               | Message Passing Communication Subsystem           | 22               |  |

|                             | 2.3.2               | MPI Communication Models                          | 22               |  |

|                             | 2.3.3               | MPI Collective Communication Algorithms           | 26               |  |

|                             | 2.3.4               | GPU-Aware MPI                                     | 30               |  |

| 2.4                         | Mode                | rn Interconnects and Communication Channels       | 31               |  |

|                             | 2.4.1               | Interconnection Networks                          | 32               |  |

|                             | 2.4.2               | Communication Channels                            | 33               |  |

| Chapte                      | er 3:               |                                                   |                  |  |

|                             |                     | Efficient GPU Collective Communication Algorithms | 36               |  |

| 3.1                         |                     | ed Work                                           | 38               |  |

| 3.2                         | GPU-                | aware Collective Communication Algorithms         | 40               |  |

|        | 3.2.1  | GPU Shared Buffer-Aware Design (GSB)                            | 41         |

|--------|--------|-----------------------------------------------------------------|------------|

|        | 3.2.2  | GPU-Aware Binomial Tree Based Design (BTB)                      | 46         |

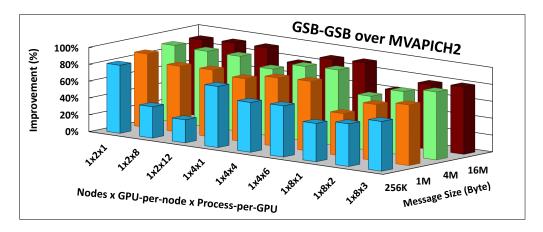

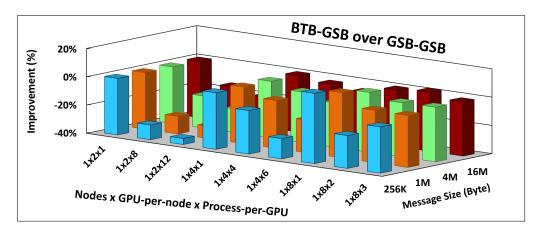

|        | 3.2.3  | Cluster-wide Extension of the GSB and BTB Algorithms            | 50         |

| 3.3    | Exper  | imental Results and Analysis                                    | 51         |

|        | 3.3.1  | Experimental Platform                                           | 51         |

|        | 3.3.2  | Single-Node Single-GPU Results                                  | 52         |

|        | 3.3.3  | Initialization Overhead:                                        | 56         |

|        | 3.3.4  | Cluster-Wide Results                                            | 57         |

| 3.4    |        | lary                                                            | 57         |

| CI.    | ,      |                                                                 |            |

| Chapte | er 4:  |                                                                 |            |

|        |        | Hierarchical Framework for GPU Collective Communi-              |            |

| 4.4    | D 1 +  | cations                                                         | 60         |

| 4.1    |        | ed Work                                                         | 62         |

| 4.2    |        | chical Collective Framework for a Multi-GPU Node and GPU        |            |

|        | Cluste |                                                                 | 64         |

|        | 4.2.1  | Designs for a Multi-GPU Node                                    | 64         |

|        | 4.2.2  | Designs for a GPU Cluster                                       | 67         |

| 4.3    |        | imental Results and Analysis                                    | 71         |

|        | 4.3.1  | Experimental Platform                                           | 71         |

|        | 4.3.2  | Results on a Single Multi-GPU Node                              | 71         |

|        | 4.3.3  | Results on a Cluster of Multi-GPU Nodes                         | 74         |

| 4.4    | Summ   | ary                                                             | 76         |

| Chapte | er 5:  |                                                                 |            |

| •      |        | Efficient GPU Communications through Smart Data                 |            |

|        |        | Copy Mechanism Selection                                        | <b>7</b> 8 |

| 5.1    | Motiv  | ation                                                           | 81         |

|        | 5.1.1  | Impact of MPS and Hyper-Q on Communication                      | 81         |

| 5.2    | Relate | ed Work                                                         | 84         |

| 5.3    | GPU    | Collective Designs with Efficient Data Copy Mechanism Selection | 86         |

|        | 5.3.1  | Static Hyper-Q Aware Algorithm                                  | 87         |

|        | 5.3.2  | Dynamic Hyper-Q Aware Algorithm                                 | 88         |

|        | 5.3.3  | Cluster-wide Extension of the Static and the Dynamic Algorithms | 95         |

| 5.4    | Exper  | imental Results and Analysis                                    | 97         |

|        | 5.4.1  | Experimental Platform                                           | 98         |

|        | 5.4.2  | Node-wide Experimental Results                                  | 99         |

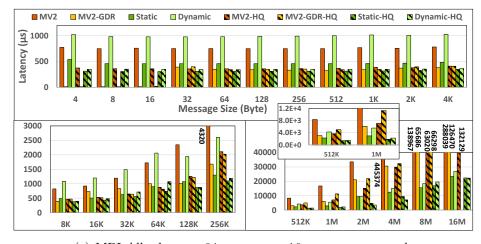

|        | 5.4.3  |                                                                 | 104        |

|        | 5.4.4  | Comparative Analysis of Hyper-Q Aware Algorithms against        |            |

|        |        | - , , , , , , , , , , , , , , , , , , ,                         | 107        |

| 5.5              | Provis          | ion of Using Our Proposals with Future GPU Accelerators     | 109  |

|------------------|-----------------|-------------------------------------------------------------|------|

| 5.6              | Summ            | ary                                                         | 112  |

| Chapte           | er 6:           |                                                             |      |

| _                |                 | Topology-aware GPU Communications                           | 114  |

| 6.1              | Motiva          | ation                                                       | 117  |

|                  | 6.1.1           | Impact of CPU/GPU Topology Levels on CPU/GPU Commu-         |      |

|                  |                 | nication Performance in a Cluster with multi-GPU nodes      | 117  |

| 6.2              | Relate          | d Work                                                      | 121  |

| 6.3              | Impro           | ving GPU Communication by Efficient GPU Assignment Scheme   | s122 |

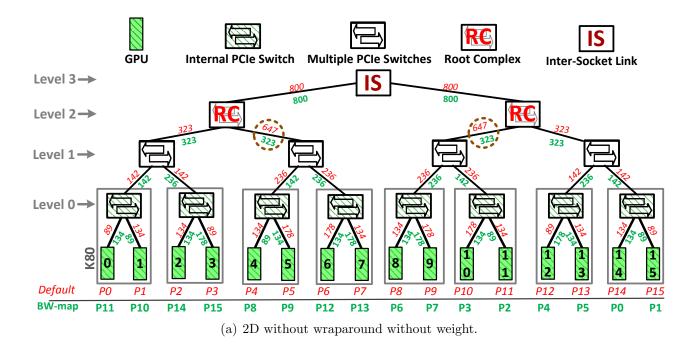

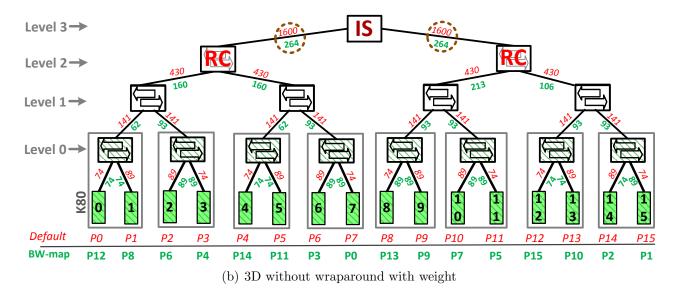

|                  | 6.3.1           | GPU Assignment Scheme on a Multi-GPU Node                   | 123  |

|                  | 6.3.2           | GPU Assignment Scheme Across the GPU Cluster                | 126  |

| 6.4              | Experi          | imental Results and Analysis                                | 129  |

|                  | 6.4.1           | Experimental Platform                                       | 129  |

|                  | 6.4.2           | Multi-GPU Node Results and Analysis                         | 129  |

|                  | 6.4.3           | GPU Cluster Results and Analysis                            | 146  |

| 6.5              | Provis          | ion of Using our Proposals with Future GPU Accelerators and |      |

|                  | Cluste          | rs                                                          | 151  |

| 6.6              | Summ            | ary                                                         | 153  |

| $\mathbf{Chapt}$ | er 7:           | Conclusions and Future work                                 | 156  |

| 7.1              | Future          | e Work                                                      | 161  |

| Bibliog          | Bibliography 10 |                                                             |      |

## List of Tables

| 6.1 | Microbenchmark specification                                     | 149 |

|-----|------------------------------------------------------------------|-----|

| 6.2 | Uni-directional bandwidth of different GPU pairs in a 4-GPU node |     |

|     | with Pascal P100 and NVLink interconnect                         | 152 |

## List of Figures

| 2.1 | Message passing communication diagram                                 | 23 |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Well-known MPI collective algorithms                                  | 29 |

| 2.3 | The node interconnection, topology tree                               | 34 |

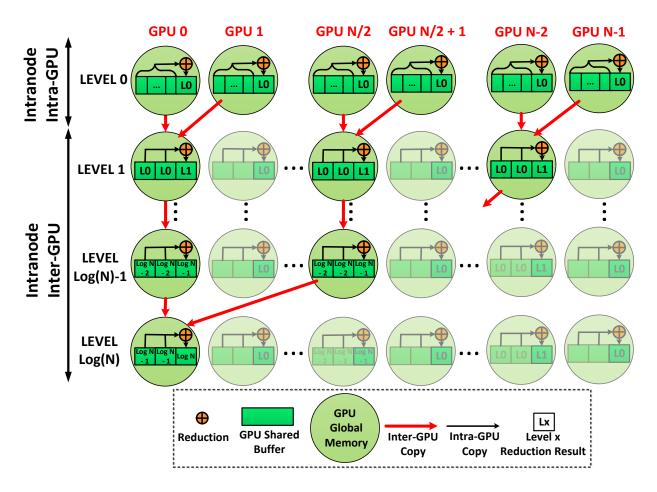

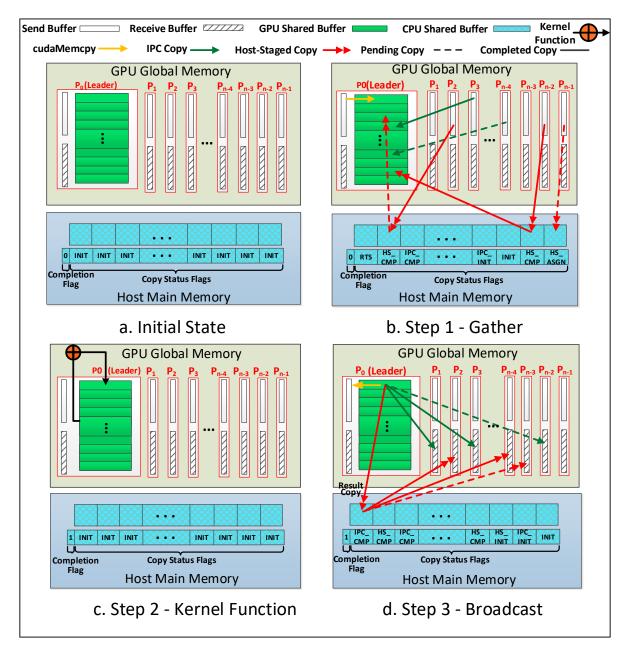

| 3.1 | Steps of the GPU shared-buffer aware approach for MPI_All<br>reduce   | 44 |

| 3.2 | Steps of the GPU-aware MPI_Allreduce using the BTB design             | 47 |

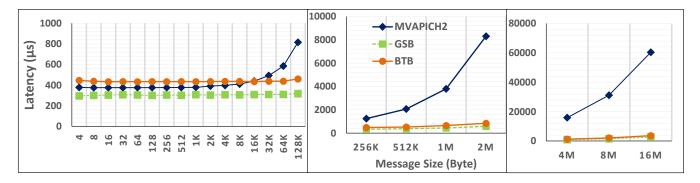

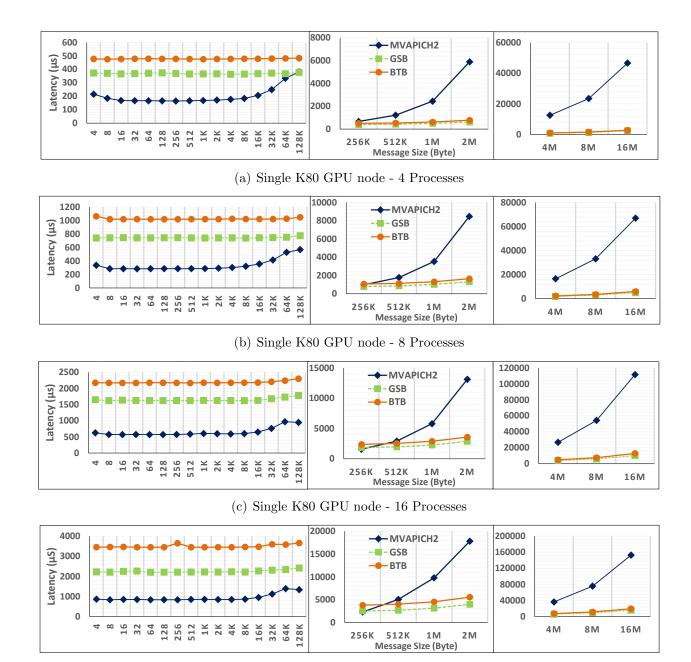

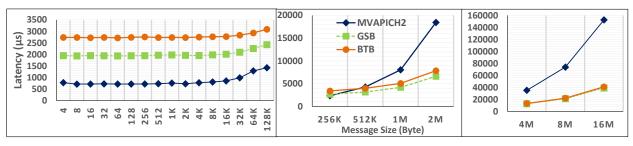

| 3.3 | MVAPICH2 vs. GSB MPI_Allreduce vs. BTB MPI_Allreduce on a             |    |

|     | single K20 node (System A) with a single GPU                          | 54 |

| 3.4 | MVAPICH2 vs. GSB MPI_Allreduce vs. BTB MPI_Allreduce on a             |    |

|     | single K80 node (System B) with a single GPU                          | 55 |

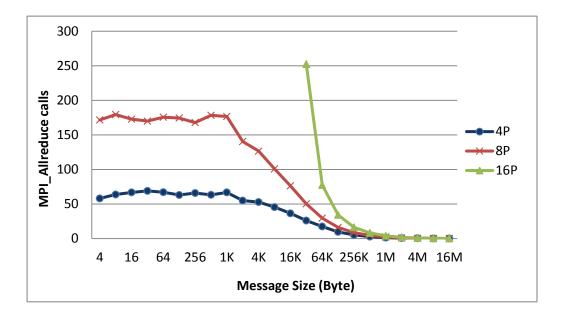

| 3.5 | Number of MPI_Allreduce calls required to compensate for the initial- |    |

|     | ization overhead                                                      | 56 |

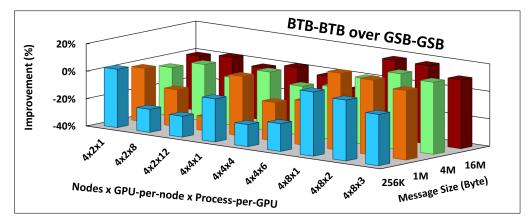

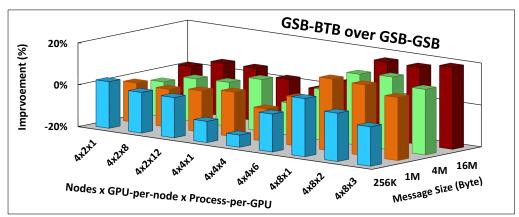

| 3.6 | MVAPICH2 vs. GSB MPI_Allreduce vs. BTB MPI_Allreduce on 4             |    |

|     | K80 node Helios cluster (System B) with single GPU per node           | 58 |

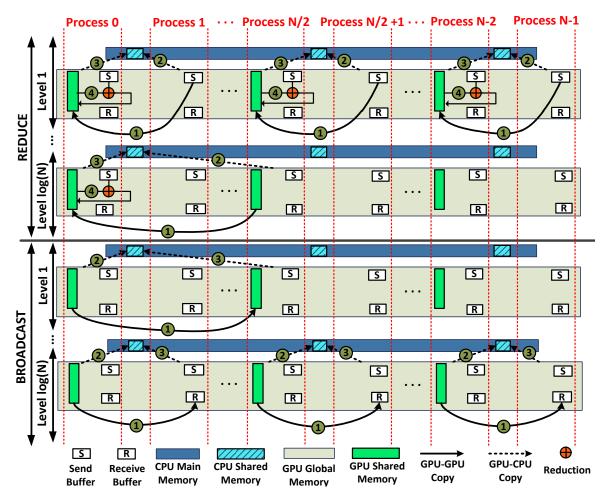

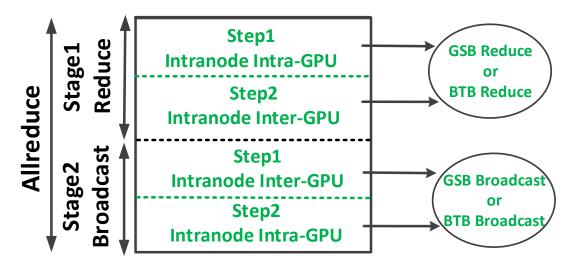

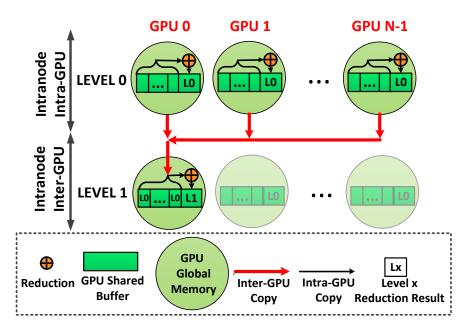

| 4.1 | Steps of the hierarchical GPU-Aware MPI_Allreduce on a multi-GPU      |    |

|     | node                                                                  | 66 |

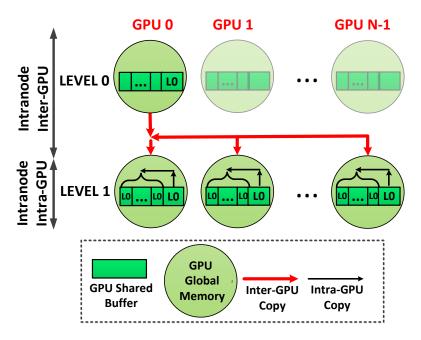

| 4.2 | Hierarchical MPI_Allreduce utilizing Intranode Intra-GPU GSB Re-      |    |

|     | duce and Intranode Inter-GPU GSB Reduce algorithms - Reduce stage     | 67 |

| 4.3 | Hierarchical MPI_Allreduce utilizing Intranode Intra-GPU GSB and       |    |

|-----|------------------------------------------------------------------------|----|

|     | Intranode Inter-GPU BTB Reduce algorithms - Reduce stage               | 68 |

| 4.4 | Hierarchical MPI_Allreduce utilizing Intranode Intra-GPU GSB Broad-    |    |

|     | cast and Intranode Inter-GPU GSB Broadcast algorithms - Broadcast      |    |

|     | stage                                                                  | 69 |

| 4.5 | Steps of the hierarchical GPU-Aware MPI_Allreduce on GPU clusters      |    |

|     | with multi-GPU nodes                                                   | 70 |

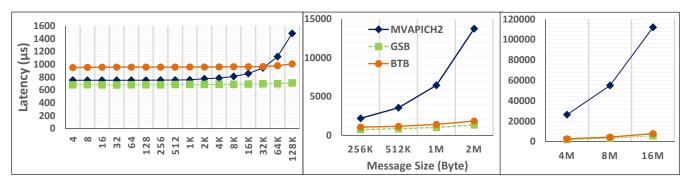

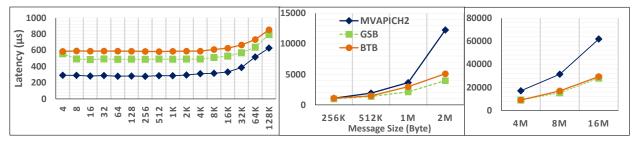

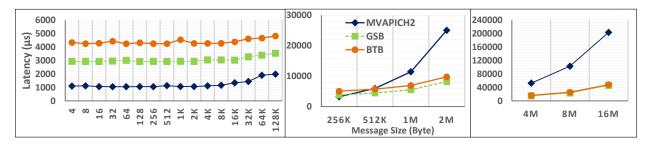

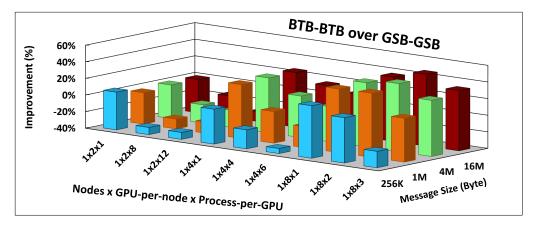

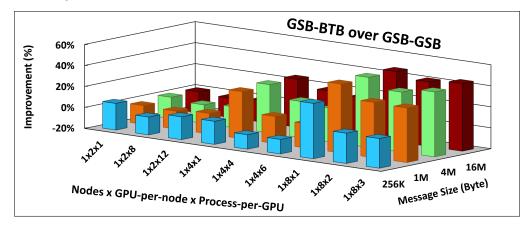

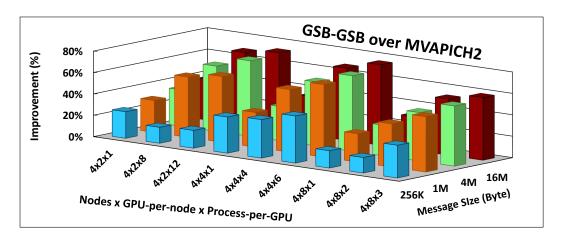

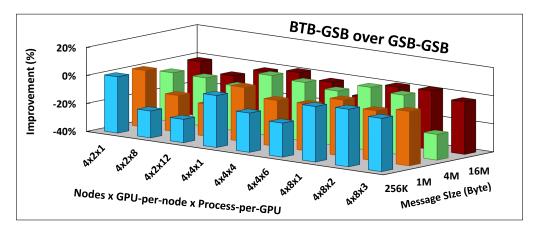

| 4.6 | GPU hierarchical MPI_Allreduce with GSB for Intranode Intra-GPU        |    |

|     | and GSB for Intranode Inter-GPU steps over MVAPCIH2 on a single        |    |

|     | Helios K80 node with multiple GPUs                                     | 72 |

| 4.7 | Evaluating the effect of using different algorithms in the GPU hier-   |    |

|     | archical MPI_Allreduce on a a single Helios K80 node with multiple     |    |

|     | GPUs per node                                                          | 73 |

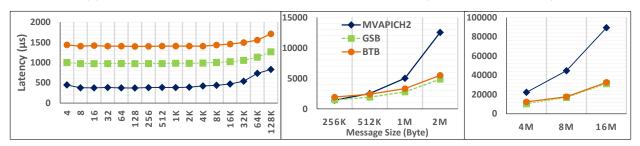

| 4.8 | GPU Hierarchical MPI_Allreduce with GSB for Intranode Intra-GPU        |    |

|     | and GSB for Intranode Inter-GPU steps over MVAPCIH2 MPI_Allreduce      |    |

|     | on four Helios K80 nodes with multiple GPUs per node                   | 74 |

| 4.9 | Evaluating the effect of using different algorithms in the GPU hierar- |    |

|     | chical MPI_Allreduce on four Helios K80 nodes with multiple GPUs       |    |

|     | per node                                                               | 75 |

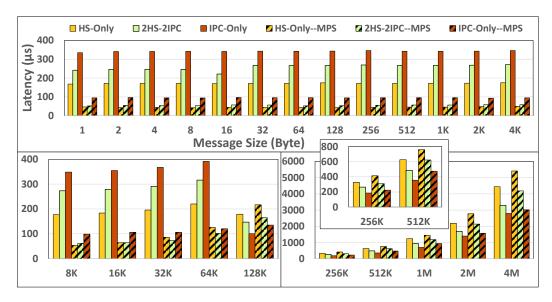

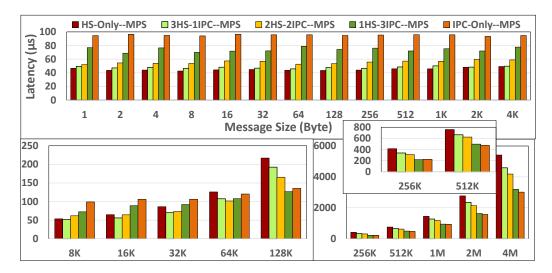

| 5.1 | Hyper-Q effect on intranode point-to-point communication with and      |    |

| 0.1 | · · ·                                                                  | 02 |

|     | without MPS                                                            | 83 |

| 5.2 | Hyper-Q effect on intranode point-to-point communication with MPS      |    |

|     | enabled                                                                | 84 |

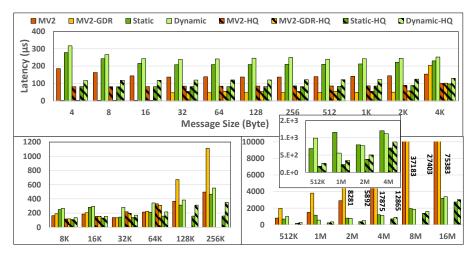

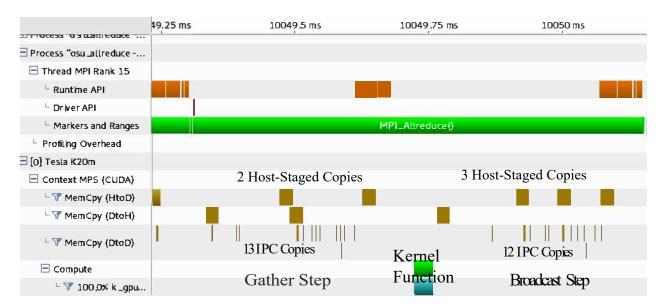

| 5.3 | Different steps of the node-wide $Dynamic$ algorithm for MPI_Allreduce | 93 |

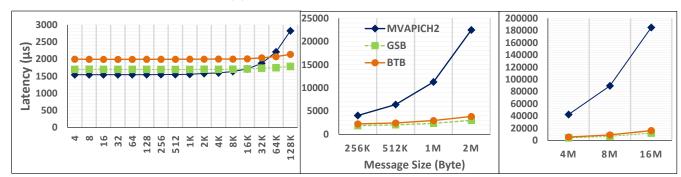

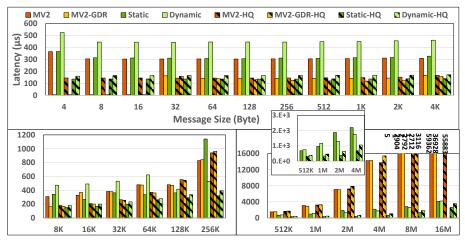

| 5.4  | $Static$ and $Dynamic$ algorithms across the cluster for MPI_Reduce                                             | 97    |

|------|-----------------------------------------------------------------------------------------------------------------|-------|

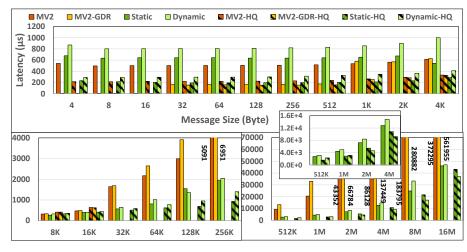

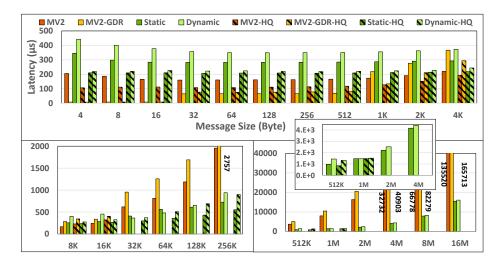

| 5.5  | $Static \ { m and} \ Dynamic \ { m vs.} \ \ { m MVAPICH2} \ { m and} \ \ { m MVAPICH2-GDR} \ { m MPI\_Allgath}$ | ner   |

|      | w and w/o the MPS on a single node of Odin cluster with a single GPU                                            |       |

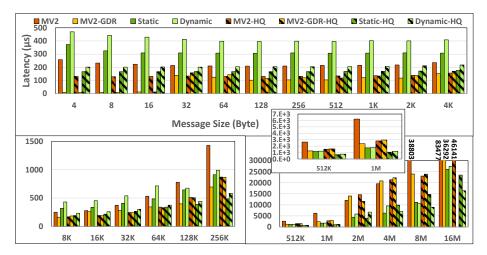

|      | per node                                                                                                        | 100   |

| 5.6  | Static and Dynamic vs. MVAPICH2 and MVAPICH2-GDR MPI_Allredu                                                    | ice   |

|      | w and w/o the MPS on a single node of Odin cluster with a single GPU                                            |       |

|      | per node                                                                                                        | 103   |

| 5.7  | Profiling snapshot of the <i>Dynamic</i> algorithm in MPI_Allreduce with                                        |       |

|      | MPS                                                                                                             | 105   |

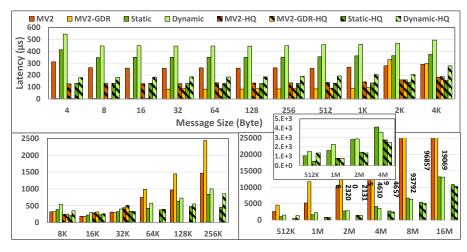

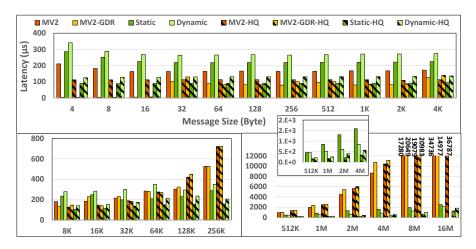

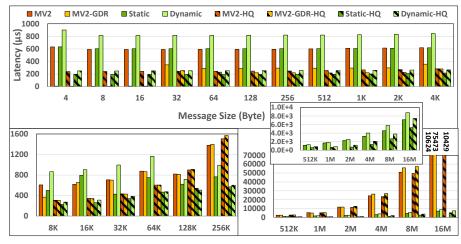

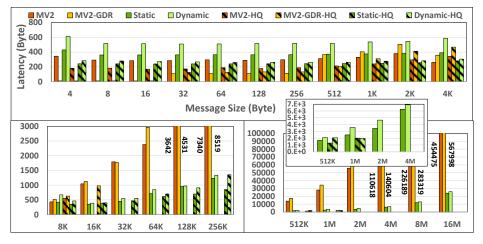

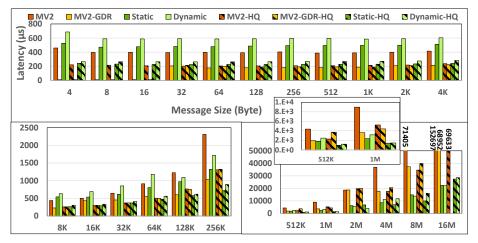

| 5.8  | Comparison of Static, Dynamic, MVAPICH2, and MVAPICH2-GDR                                                       |       |

|      | using MPI_Allgather w and w/o the MPS on 4 nodes with a single                                                  |       |

|      | GPU per node                                                                                                    | 106   |

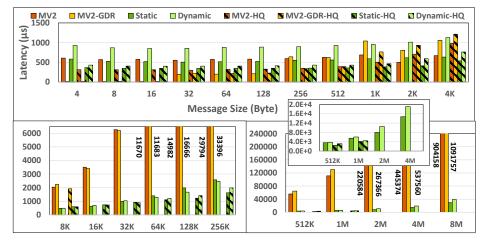

| 5.9  | Comparison of Static, Dynamic, MVAPICH2, and MVAPICH2-GDR                                                       |       |

|      | using MPI_Allreduce w and w/o the MPS on 4 nodes with a single                                                  |       |

|      | GPU per node                                                                                                    | 108   |

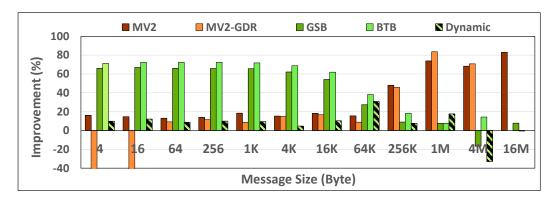

| 5.10 | Improvement percentage of the <i>Static</i> approach over MVAPCIH2, MVAP                                        | ICH2- |

|      | GDR, GSB, and BTB for MPI_Allreduce with 64 processes using MPS                                                 |       |

|      | - System C with 4 nodes and a single GPU per node                                                               | 109   |

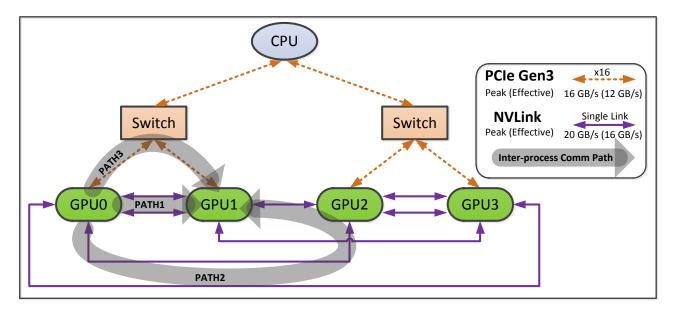

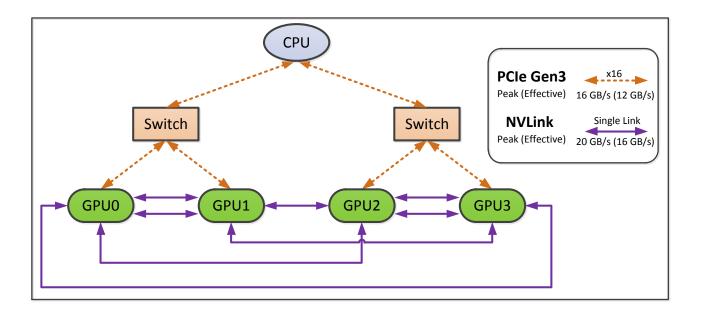

| 5.11 | Different intranode communication channels of a 4-GPU node with                                                 |       |

|      | NVLink and PCIe (adapted from [66])                                                                             | 111   |

|      |                                                                                                                 |       |

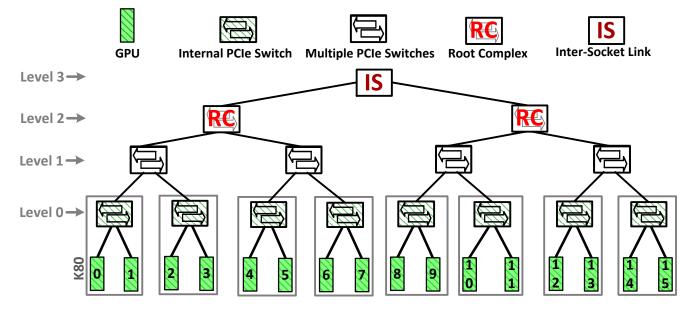

| 6.1  | Different intranode GPU pair levels. This is also the topology of the                                           |       |

|      | K80 GPU node used in our experiments                                                                            | 118   |

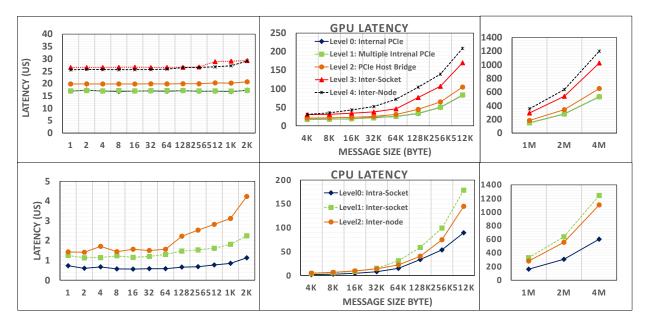

| 6.2  | Impact of internode and intranode CPU and GPU topology level on                                                 |       |

|      | ping-ping latency in a GPU cluster                                                                              | 120   |

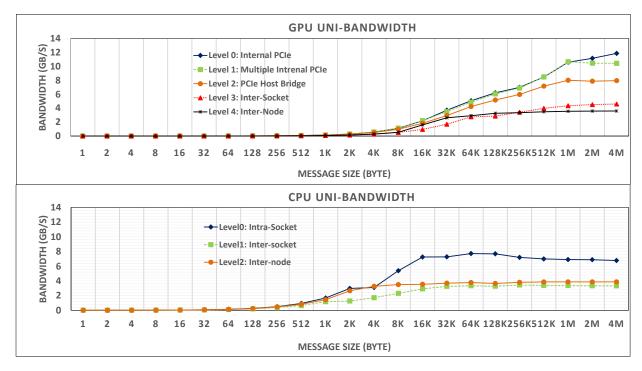

| 6.3  | Impact of internode and intranode CPU and GPU topology level on                   |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | uni-directional bandwidth in a GPU cluster                                        | 120 |

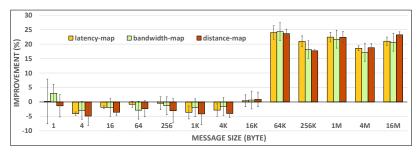

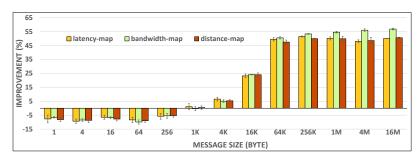

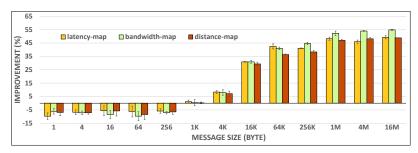

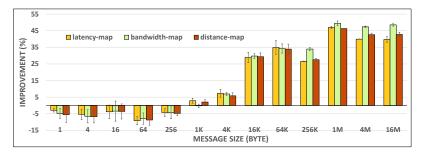

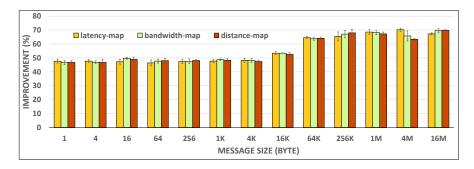

| 6.4  | Communication time improvements achieved by topology-aware GPU                    |     |

|      | selection over the default selection scheme for the non-weighted 2D and           |     |

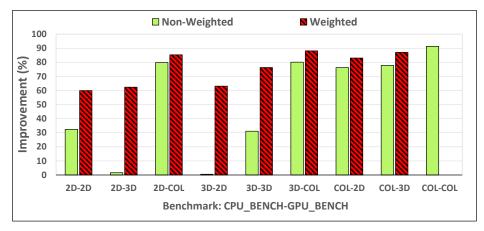

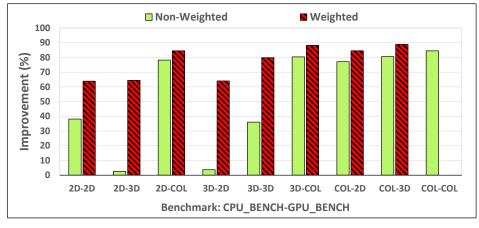

|      | 3D microbenchmarks                                                                | 132 |

| 6.5  | Communication time improvements achieved by topology-aware GPU                    |     |

|      | selection over the default selection scheme for the weighted 2D and 3D            |     |

|      | microbenchmarks                                                                   | 133 |

| 6.6  | Communication time improvements achieved by topology-aware GPU                    |     |

|      | selection over the default selection scheme for the sub-communicator              |     |

|      | collective microbenchmark, COLL                                                   | 134 |

| 6.7  | Congestion values for the default and topology-aware GPU assignment               | 137 |

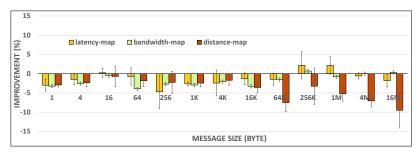

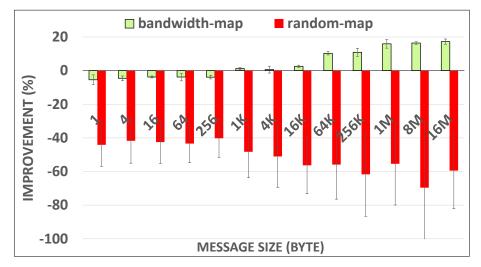

| 6.8  | Communication time improvements achieved by topology-aware GPU                    |     |

|      | selection and random mapping over the default selection scheme                    | 139 |

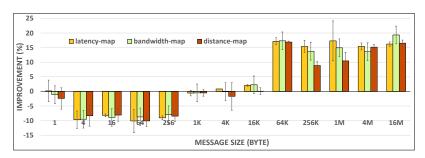

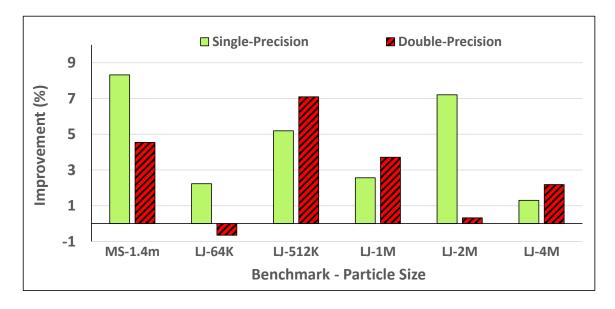

| 6.9  | TPS improvement of topology-aware mappings over default mapping                   |     |

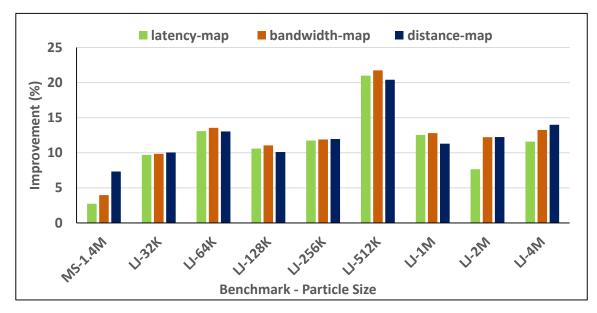

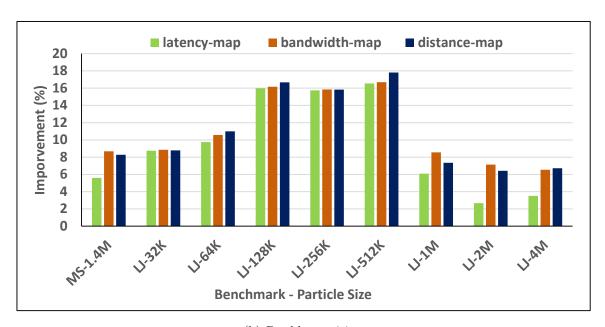

|      | on a) single-precision and b) double-precision HOOMD-blue Application             | 141 |

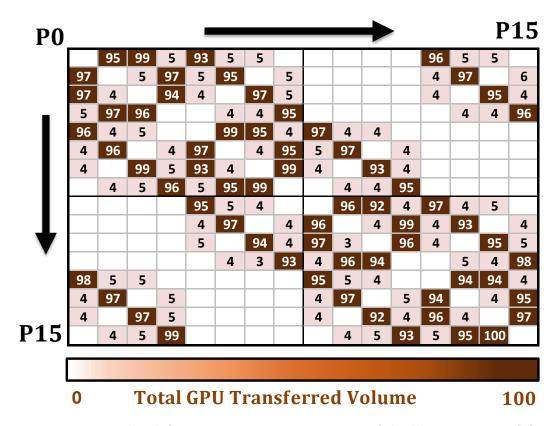

| 6.10 | Normalized GPU communication pattern of double-precision HOOMD-                   |     |

|      | Blue with LJ-512K benchmark                                                       | 143 |

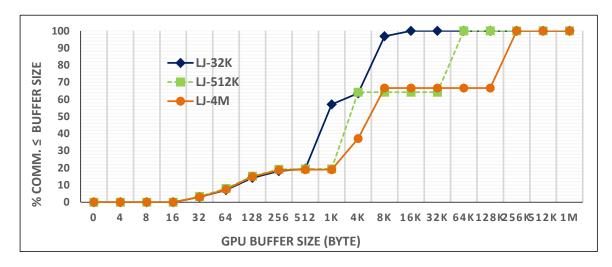

| 6.11 | Distribution of different message sizes in GPU communications of double-          |     |

|      | precision HOOMD-Blue with LJ benchmark                                            | 144 |

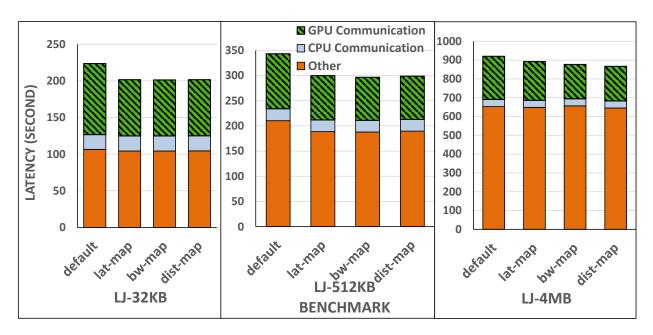

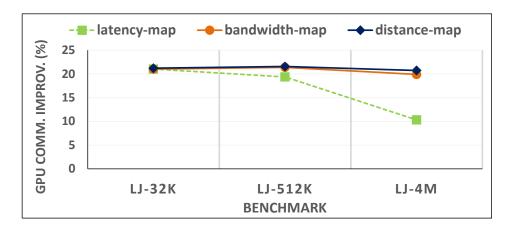

| 6.12 | Share of GPU Communications in total HOOMD-Blue runtime                           | 145 |

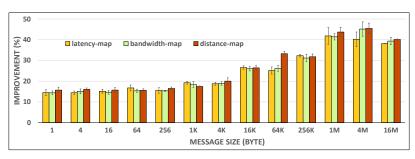

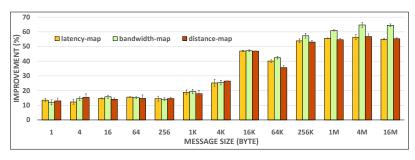

| 6.13 | HOOMD-Blue GPU communication improvements                                         | 145 |

| 6.14 | ${\bf Microbenchmark\ runtime\ improvements\ using\ a\ 3-phase\ mapping\ frame-}$ |     |

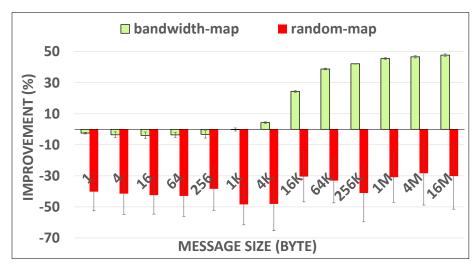

|      | work on various message sizes over the default selection scheme                   | 148 |

| 6.15 | HOOMD-blue TPS (number of application time steps per second) im- |     |

|------|------------------------------------------------------------------|-----|

|      | provements using a topology-aware scheme on various benchmarks   | 151 |

| 6.16 | Node architecture of a 4-GPU node with Pascal GPUs and NVLink    |     |

|      | interconnect (adapted from [66])                                 | 153 |

## List of Abbreviations

**BTB** Binomial Tree Based

CFD Computational Fluid Dynamic

CPU Central Processing Unit

CUDA Compute Unified Data Architecture

**ECC** Error Correcting Code

ExaFLOP 10<sup>18</sup> FLoating-point Operations Per Second

FLOPS FLoating-point Operations Per Second

**GPU** Graphics Processing Units

**GSB** GPU Shared Buffer

**HCA** Host Channel Adapter

**HPC** High Performance Computing

**IB** InfiniBand

**IPC** Inter-Process Communication

MD Molecular Dynamic

MPI Message Passing Interface

MPP Massively Parallel Processor

MPS Multi Process Service

NIC Network Interface Card

**NVCC** NVIDIA C Compiler

**NVML** NVIDIA Management Library

**NVPROF** NVIDIA Profiler

$\mathbf{NVTX}$  NVIDIA Tools Extension

**NVVP** NVIDIA Visual Profiler

OpenCL Open Computing Language

**OS** Operating System

**RDMA** Remote Direct Memory Access

PCIe Peripheral Component Interconnect Express

**PetaFlops**  $10^{15}$  FLoating-point Operations Per Second

**RMA** Remote Memory Access

SIMT Single Instruction Multiple Thread

SM Steaming Multiprocessor

**SP** Steaming Processor

$\mathbf{TPS}$  Time Steps Per Second

## Chapter 1

## Introduction

High-performance computing (HPC) refers to aggregating the computational power of different processing units to deliver high performance for running challenging applications. These applications can span across different areas such as Molecular Dynamic (MD) simulation in chemistry [27, 18], Computational Fluid Dynamic (CFD) [67] and thermodynamics [45] in physics, N-Body simulations in cosmology [31], and training using deep learning in applications such as speech recognition [14, 2], to name a few. Massive computational power provided by HPC is a key requirement for the high performance calculations and trainings of these applications.

Clusters are the predominant architecture for HPC systems; according to the TOP500 list of the world's most powerful supercomputers [91], 432 of the top 500 supercomputers are clusters. A computer cluster consists of a number of computing systems that are loosely coupled through a high speed interconnection network. The key advantage of the cluster architecture is that it provides high performance with

high degree of availability, and relatively lower cost compared to the alternative architectures, such as massively parallel processors (MPP)<sup>1</sup>. The node architecture of a modern HPC cluster typically consists of multi-core processors, co-processors, and accelerators. GPUs, among other co-processors and accelerators, have successfully established themselves in HPC clusters due to their high performance and energy efficiency. These factors are the key requirements of the future supercomputers, thus paving the way for GPUs to be continually used in current petaflop (10<sup>15</sup> FLoating-point Operations Per Second) and future exascale (10<sup>18</sup> FLOP) systems. As a matter of fact, the two next 100+ petaflops supercomputers announced by the CORAL program [20] (i.e., Sierra [83] and Summit [89]) will use GPUs and move the world closer to exascale.

GPUs are composed of thousands of processing units, and use a data-parallel model to distribute the application dataset among them to parallelize and accelerate computation. The massive computational capability of the GPU hardware makes it a good candidate to offload and accelerate compute-intensive portions of the applications running on HPC clusters.

Inter-process communication is one of the key factors in determining the performance of HPC applications. Different processes may communicate with each other using different programming models, such as shared memory or message passing model. The message passing programming model provides higher scalability and thus is considered as the main programming model for high-end computing systems. The Message Passing Interface (MPI) [56] is the de-facto standard for the message passing programming model. In HPC clusters with GPU accelerators, while computation can

<sup>&</sup>lt;sup>1</sup>Although our proposals in this dissertation are evaluated on GPU-accelerated HPC clusters, they can also be adapted and used on the GPU-accelerated MPP architectures.

be offloaded and accelerated on the GPUs, support from MPI library is required to allow processes to communicate the data residing in GPU memory.

While GPUs can accelerate the offloaded computation, inefficient GPU-to-GPU communications may wipe out the benefits of offloading in the first place. Consequently, efficient usage of GPU accelerators in HPC clusters demands both efficient GPU computations and inter-process communications. In this dissertation, we seek to improve GPU inter-process communication performance by improving communication latency/bandwidth and application communication efficiency (communication efficiency in short). Communication latency refers to the inter-process communication time, and communication bandwidth refers to the message volume transferred per second. Improving communication efficiency refers to improving the total application communication performance involving all GPU inter-process communications. For example, application communication efficiency can be improved by overlapping different GPU inter-process communications or by efficiently assigning GPUs to processes, while the latency or bandwidth of individual GPU inter-processes communications may not be necessarily improved.

There are different ways to improve the performance of GPU inter-process communications; this includes devising efficient GPU-aware designs and algorithms, designs that are aware of the topology of the GPU clusters, as well as exploiting advanced GPU hardware features. In this dissertation, we use various combinations of these approaches to propose designs that seek to improve the performance of GPU interprocess communications.

#### 1.1 Problem Statement

In MPI, processes can pass messages to each other using three different communication models: 1) point-to-point; 2) collective; and 3) Remote Memory Access (RMA). In point-to-point, a pair of processes communicate with each other in a cooperative fashion. Collective operations, on the other hand, involve communications among two or more processes. In RMA, a process is involved in a one-sided communication. The current MPI standard is developed for systems with multiple CPUs and no accelerators. With the emergence of GPU accelerators, MPI need to evolve to provide efficient support for such accelerators. Integrating GPU awareness into communication runtime libraries requires careful designs and optimizations that are specific to the GPU architectures. It is therefore crucial to understand that such designs and optimizations do not have to necessarily follow the designs that work efficiently on traditional CPU clusters. This is due to the fact that CPUs and GPUs have different architecture, hardware features, and programming model. On the other hand, GPU devices, similar to multi-core CPUs, use a hierarchy of communication channels to interconnect with each other. However, these communication channels have different nature and physical topology. Consequently, many of the concepts that are used to improve CPU inter-process communications in homogeneous nodes and clusters cannot apply to the heterogeneous nodes and clusters and must be redesigned. Taking these into account, in this dissertation we seek to address the following questions:

- How can GPU-aware algorithms benefit MPI collective communication routines? What GPU features can be effectively used in these designs?

- Can hierarchical designs outperform the existing flat designs in MPI collective

communication performance on clusters of multi-GPU nodes? If yes, what is the sensitivity of different algorithms to different hierarchy levels and which combination of them is the most effective one?

- Which data copy mechanisms should be used for efficient GPU inter-process communications? Can multiple data copy mechanisms be used in conjunction with each other to perform multiple GPU inter-process communications and enhance collective communications?

- What are the different communication channels in a cluster of multi-GPU nodes and how does their performance vary from each other? What is the communication pattern of GPU applications and how it can be profiled? How can topology-aware designs improve the efficiency of inter-process communications in a multi-GPU node and across the GPU clusters?

#### 1.2 Contributions

This dissertation presents several proposals to improve the GPU inter-process communications in HPC clusters with GPU accelerators. It contributes by addressing several sources of inefficiencies in such communications by providing new or improved designs.

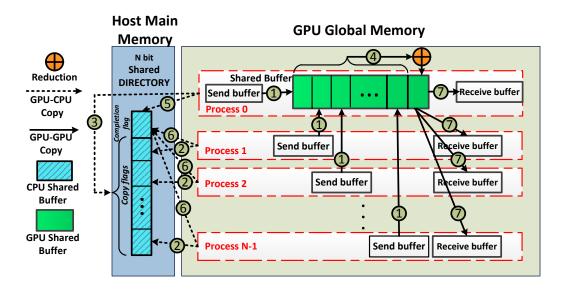

#### (1) Efficient GPU Collective Communication Algorithms

On one hand, collective communications contribute to considerable portions of MPI applications runtime [75]; on the other hand, efficient GPU inter-process communication is of crucial importance in GPU-accelerated applications [70]. Taking these into account, in Chapter 3, we propose GPU-aware algorithms [23, 22] to improve the performance of the GPU collective operations. We provide designs and

experimental results<sup>2</sup> for MPI\_Allreduce operation that involves both collective communication and computation. Our proposed algorithm can be applied to other collective communications with minor changes as well. In these designs, we also incorporate advanced GPU features for further performance improvement. The proposed designs show the importance of minimizing CPU intervention in GPU collective operations. We achieve this by proposing designs that are capable of performing inter-process communications through GPU shared memory regions, and utilizing in-GPU kernels to manipulate the collective data residing in GPU memory. Our proposed collective designs in this chapter provide up to 22 and 5 times performance improvement over the existing designs within a single-GPU node and across the cluster of single-GPU nodes, respectively.

#### (2) Hierarchical Framework for GPU Collective Communications

The contributions in Chapter 4 revolve around utilizing the hierarchical nature of HPC clusters with multi-GPU nodes. This chapter proposes a hierarchical framework for collective communication operations in clusters of multi-GPU nodes [22]. The proposed hierarchical framework breaks down the collective operations into different stages. Operations within each stage are performed on a single hierarchy level. This chapter evaluates the effect of different algorithms within different hierarchy levels. It also shows that by choosing the right set of algorithms in the hierarchal framework, collective communication operations can highly outperform the native flat designs. Using our hierarchical framework, we provide up to 80% and 65% performance improvement on MPI\_Allreduce over the existing flat designs within a multi-GPU node and across the cluster of multi-GPU nodes, respectively.

<sup>&</sup>lt;sup>2</sup>In this dissertation, all result are reproducible by following the proposed design steps and using the same environment and settings.

## (3) Efficient GPU Communications through Smart data copy mechanism Selection

Chapter 5 first evaluates the impact of using different data copy mechanisms on GPU inter-process communications. Depending on the GPU communication characteristics such as the message size, one data copy mechanism is usually preferred over the other. We then provide evidence that multiple GPU inter-process communications can take advantage of jointly using different data copy mechanisms. Accordingly, this chapter proposes alternative designs for GPU collective operations that use different data copy mechanisms to perform collective operations [24, 22]. The proposed designs are capable of efficiently deciding the data copy mechanisms based on the information that they gather either during or prior to the runtime. The main contribution of this chapter is to show the potential of using different GPU data copy mechanisms with different communication channels to speedup the total GPU inter-process communications. Using our proposals, we show up to 2.62 times speedup in the total GPU inter-process communications.

#### (4) Topology-aware GPU Communications

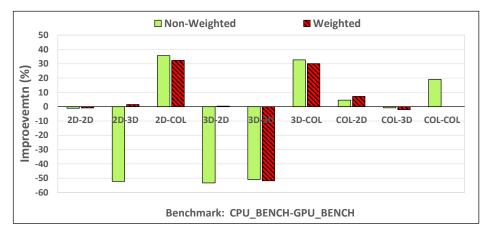

Chapter 6 first provides a comprehensive evaluation of different communication channels that are used for inter-process communications in multi-GPU nodes. Evaluation results show substantial performance difference among different communication channels that are interconnecting processing units in multi-GPU nodes. Accordingly, Chapter 6 presents topology-aware mapping solutions that map MPI processes to processing units in a way to improve the total inter-process communications. The proposed topology-aware designs target both single [25, 26] and clustered multi-GPU

node(s) [55]. For single-GPU nodes, we use a non-trivial topology-aware GPU selection scheme that considers the application communication pattern and the physical topology of the node. Three metrics are proposed to represent the topology of the multi-GPU nodes: 1) latency; 2) bandwidth; and 3) communication distance. This chapter also contributes by extending the topology-aware GPU selection scheme from a multi-GPU node to across the GPU cluster. In this regard, cluster-wide topology-aware communication is defined as a mapping scheme which breaks down the mapping into three distinct phases: 1) internode process-to-node mapping; 2) intranode process-to-CPU-core binding; and 3) intranode process-to-GPU assignment. Performance results show substantial improvement over native designs at both microbenchmark and application levels. On a multi-GPU node, our topology-aware proposal provide up to 72% and 21% improvement in performance at the microbenchmark and application levels, respectively. Our proposals also improve the total benchmark runtime by 90% and show up to 8% application performance improvement across the GPU cluster.

#### 1.3 Dissertation Outline

The rest of this dissertation is organized as follows. Chapter 2 provides some background materials on HPC clusters with GPUs, modern GPU architectures, and their advanced programming tools and features. This chapter also overviews the Message Passing Interface and GPU-aware MPI communication libraries. In Chapter 3, GPU-aware algorithms for improving collective operations are presented. Chapter 4 presents a hierarchical framework for GPU collectives targeting clusters of multi-GPU nodes; it also evaluates the sensitivity of different algorithms to different hierarchy

levels for these operations. Chapter 5 shows the efficiency of using different data copy mechanisms to perform multiple inter-process communications; this chapter builds on this observation and provides novel designs for GPU collective operations. In Chapter 6, we provide topology-aware solutions for efficient communication in multi-GPU nodes and clusters. Finally, Chapter 7 concludes this dissertation and outlines some future research directions.

## Chapter 2

## Background

Over the past decade, the high-performance computing landscape has changed significantly, particularly due to the emergence of accelerators. In particular, GPU accelerators have established themselves in modern heterogeneous HPC clusters by offering high performance and energy efficiency. Consequently, heterogeneous clusters with GPU accelerators have become the platform of choice for many HPC applications. In this chapter, we provide a brief overview of the HPC clusters with GPU accelerators. Then, we discuss the state-of-the-art architecture, programming model, and features of the GPU accelerators. We introduce the Message Passing Interface (MPI) as the de-facto standard for parallel programming and discuss integration of GPU-awareness into some of its implementations. Finally, we go over modern interconnects and communication channels that are typically used in HPC clusters with GPU accelerators.

#### 2.1 HPC Clusters with Accelerators

An HPC cluster is composed of a large number of independent compute nodes loosely interconnected together via an interconnection network, together providing a single

computing resource. This is in contrast to the Massively Parallel Processor architecture, where there is only one machine with all processing units tightly interconnected together usually with a custom designed interconnect. MPPs, due to their custom and proprietary design are more expensive than clusters. However, the custom design of MPPs can potentially make them a better fit for some specific applications. In this dissertation, our designs target HPC clusters with GPU accelerators.

HPC clusters benefit from high bandwidth and low latency interconnection networks due to the high demand of HPC applications for frequent communications among HPC nodes. The node architecture of modern HPC clusters consists of multicore processors and accelerators/co-processors. Accelerators/co-processors provide high compute capacity and low power dissipation, making them a promising candidate in improving the performance per watt of the HPC clusters. GPUs, compared to other accelerators and co-processors have gained the widest adoption in modern HPC clusters. This trend is continued by the announcement of Sierra and Summit, two 100+ petaflops supercomputers, in the CORAL program [20]. The high share of GPUs in HPC clusters is mainly rooted in meeting the high performance, memory bandwidth capacity, and power efficiency that is required by the compute engines of the next generation HPC clusters.

## 2.2 Graphics Processing Units (GPUs)

In this section, we introduce the architecture, programming model, and advanced hardware features of the state-of-the-art GPU accelerators. NVIDIA [62] and Advanced Micro Device (AMD) [1] are the two leading manufacturer of GPU chips.

NVIDIA GPUs, however, have higher adoption in the top500 supercomputers. According to TOP500 list, only one out of 72 supercomputers with GPU accelerators use AMD GPUs and the rest exploit NVIDIA GPUs. Taking this into account, we only target NVIDIA GPUs and perform our experiments on them. Thus, the terminologies and GPU features used in this dissertation, unless otherwise specified, only apply to the NVIDIA GPUs.

#### 2.2.1 GPU Architectures

A modern GPU architecture is assembled of an array of Streaming Multiprocessors (SM) [44]. SMs are composed of a set of Stream Processors (SPs), each executing instructions of a thread at a given time (cycle). SPs share control logic and an instruction cache, while SMs have access to the global memory. GPUs follow SIMT (Single Instruction Multiple Threads) model [47] in which a group of (currently 32) threads known as a warp execute the same instruction. Thousands of such SPs exist in modern GPU devices; this means that each GPU is capable of executing thousands of threads at any given moment. But in reality, it is possible to issue many more threads than the number of existing SPs.

#### Thread Organization:

Parallel execution on GPUs is handled by fine-grained threads. Upon GPU kernel invocation, a grid of threads is issued, all executing the same kernel. Threads in CUDA (Compute Unified Data Architecture) are organized in a two-level hierarchy: grid are at the top of the hierarchy, consisting of blocks; blocks are placed at the lower hierarchy, consisting of threads. Threads within a block have access to the shared memory and executing the same instructions, while threads between the blocks have

access to the global memory and can execute different instructions. Both threads and blocks are coordinated so individual threads can distinguish themselves among each other and detect the portion of the data they are supposed to work on. The maximum number of blocks/threads that can fit in a single grid/block is implementation dependent, and is known as gridDim (gird dimension) and blockDim (block dimension), respectively. The SM bundles a group of threads into a warp to work in an SIMT fashion; this way all of the threads within a warp require only a single control unit.

#### **GPU Memories:**

Memory access latency is one of the limiting factors in CUDA applications that undermines its computational capabilities. To address this, there exists different types of GPU memories. The GPU global memory is the slowest and most spacious GPU memory; this memory space can be accessed from the GPU that it belongs to, the host, or other peer accessible GPUs in the system. Constant memory can be read or written by the host, but threads on the device can have read-only access to it; it provides a fast, high-bandwidth access, specifically when multiple threads try to access the same location. Shared memory is a fast on-chip memory that threads on a block have access to (a portion of the shared memory, depending on the number of blocks, is assigned to each SM). Registers are also fast on-chip memories, but are allocated to single threads, so each thread can only access its pertinent register.

#### Floating-Point Units:

GPU supports single- and double-precision floating point (as well as half-precision in the latest Pascal GPU architecture) operations which has expanded the domain of supported applications on GPU devices.

#### Streams and Events:

Stream is a sequence of CUDA instructions, executed serially. After Compute Capability 2, multiple CUDA streams can run on a single GPU. An event is a dummy instruction injected into the stream. One purpose of the event is to calculate the elapsed time between events; by also synchronizing on an event, one can make sure all of the instructions before the event have already been executed.

#### 2.2.2 GPU Programming Languages and Tools

#### **GPU Programming Languages**

All of the GPU programming languages discussed here are aimed to provide an environment in which GPU and CPU programs can coexist with each other. The main goal of these programming languages is to offload the GPU friendly potion of the program into the GPU memory. To achieve this, different programming languages use different techniques and APIs. In the rest of this section, we will review three of the most popular GPU programming languages, namely CUDA [61], OpenCL [88], and OpenACC [103].

CUDA: CUDA (Compute Unified Device Architecture) [61] is an extension to ISO C, developed by the NVIDIA Corporation [62]. One way to look at a CUDA program is to consider it as C code which only includes host code. To make use of the GPU resources, the code can be optimized by adding device keywords and APIs. The CUDA compiler is called NVCC (NVIDIA C Compiler) and is responsible for separating the host code and the device code to be compiled by the C compiler and the runtime component of NVCC, respectively. In this dissertation, we use CUDA as our programming platform.

OpenCL: OpenCL [88] is another GPU programming language, designed for heterogeneous systems. OpenCL was initiated by Apple and maintained by the non-profit technology consortium Khronos Group [58], and has been adopted by Intel, AMD and NVIDIA. OpenCL is fundamentally the same as CUDA and in most cases there is a one-to-one correspondence between their features. Like CUDA, OpenCL is also based on the C language and targets heterogeneous systems. Unlike CUDA, OpenCL is not platform-, vendor-, or hardware-specific. Portability of OpenCL across various platforms and hardware does not come at no cost. It inevitably requires incorporating complex device management model and would require optional features that only specific devices can use.

OpenACC: The OpenACC specification [103] is provided by a non-profit foundation which is initially formed by Portland Group Inc. (PGI), Cray Inc., and NVIDIA. The goal of OpenACC is to provide an environment for the scientists to easily accelerate their programs using directives. OpenACC APIs are, in general, a set of compiler directives and library routines that can be used to specify loops or other regions of the code to be offloaded to the accelerator devices, including GPUs. OpenACC unlike CUDA and OpenCL, removes the burden of initializing the kernel and associated data movement from the user, leaving these heavy lifting details to the compiler and the runtime library. However, like CUDA and OpenCL, the programmer is still responsible for recognizing parallelizable regions of the code and has to specify the data that is going to be locally available to the accelerator. OpenACC compared to the other two aforementioned programming languages is attractive in such a way that it provides less barriers for heterogeneous programmers to utilize accelerators. On the other hand, OpenACC directives just provide some hints from the programmer,

and efficient use of the accelerator is up to the compiler while CUDA/OpenCL relies less on the compiler as parallelism is explicitly mentioned by the programmer. In a nutshell, in CUDA/OpenCL, programmers have more flexibility to exploit the accelerator resources.

In this dissertation, we only use the CUDA programming language which is specifically tuned for NVIDIA GPUs. We use NVIDIA GPU features (e.g., Hyper-Q), tools (e.g., NVIDIA profiling tool), and libraries (e.g., NVIDIA management library) to monitor and enhance the efficiency of our proposals. However, none of these tools is required to implement our proposed designs in other programming libraries, such as OpenCL. Our designs in CUDA can be potentially converted to OpenCL using CUDA-to-OpenCL translator, such as CU2CL [51], which provides source-to-source translation of CUDA to OpenCL codes.

#### **GPU** programming Tools

NVIDIA Management Library: The NVIDIA Management Library (NVML) [63] includes a set of C-based APIs that can be used for extracting various states and characteristics of the NVIDIA GPU devices, including monitoring, managing and querying the GPU states and topology information. The NVML library can be used to query various GPU states and information. Some of the query-able states include the GPU performance state, current GPU core temperature and board power draw, and GPU resource/memory utilization. The NVML library also allows the user to modify various GPU states. Some of the modifiable states include, enabling/disabling Error Correcting Code (ECC), changing the GPU compute mode (to control whether compute processes can run exclusively or concurrently with other processes). The

NVML library also provides a set of APIs to retrieve some information from the GPU(s). Some of this retrievable information includes, the GPU BUSID/UUID, and the topology information. Moreover, NVML provides APIs to retrieve the GPU topology information of the node. For instance, the topology API function nvmlDeviceGetTopologyCommonAncestor() can be used to find the common ancestor in a GPU pair. The retrieved common ancestor value represents the node level relationship between two GPUs (the larger this value, the higher the topology level between the GPUs would be). The nvmlDeviceGetTopologyNearestGPUs() is another example of NVML topology API, which provides a set of GPUs that are nearest to a given GPU at a specific interconnectivity level. We use NVML topology APIs in Chapter 6 to extract the topology information of the multi-GPU node.

#### **GPU Profiling Tools**

GPU Profiling tools and APIs allow one to better understand and optimize the GPU computation and communication performance of HPC applications.

NVIDIA Profiling Tools: NVIDIA provides a set of profiling tools and libraries [65] to trace the CPU and GPU activities of the application. The NVIDIA Visual Profiler (NVVP) is a graphical profiling tool that provides a timeline to demonstrate these activities. The NVIDIA Profiler (NVPROF) allows to collect and view the application profiling data from the command-line. With NVVP and NVPROF, one can collect and show the trace of the application GPU calls that are made by the CPU threads. However, in order to understand what tasks are being performed by the CPU threads outside of the GPU function calls, the NVIDIA Tools Extension API (NVTX) can be used. By adding the NVTX markers and ranges to the application, the Timeline View is capable of showing both the CPU and GPU activities that are being executed

by the CPU threads. More specifically, we use NVTX to annotate MPI routines, and assign MPI ranks to their associated process ids and GPU contexts on the profiler timeline. We also use NVPROF to present an overview of the instructions launched by the CUDA runtime or driver API. The log file provided by the NVPROF and NVTX is eventually fed to NVVP which provides a trace of the CPU and GPU activities of the application. We use NVIDIA profiling libraries in Chapter 5 to profile how different data copy mechanisms are used in our proposed designs for GPU collective operations.

GPU-Aware FPMPI Profiling library: FPMPI [29] is a profiling library which provides various information about the underlying MPI (MPI will be discussed in Section 2.3) communications of an application. Such information, in general, can be categorized into three groups: 1) synchronization data; 2) asynchronous communication data; and 3) topology data. The synchronous communication routines provide some related profiling data, while the asynchronous data lists the asynchronous communication routines. The topology data provides a brief output of the communication topology. While FPMPI is capable of providing such profiling information, it does not distinguish between the CPU and GPU communications. In other words, FPMPI provides one list of profiling data for all MPI routines regardless of where their associated communication buffer is allocated. In this regard, we have extended the FPMPI library to provide profiling support for both CPU and GPU communications. The extended profiler allows us to separately extract the CPU and GPU communication characteristics of an application. To this end, we leverage various CUDA APIs to analyze the buffer(s) in MPI routines. By analyzing the buffer(s), we can determine whether it is located on the host main memory or on the GPU global memory. We also instrument Open MPI [68] to expose specific information that will be queried by the FPMPI library. For instance, we add the address type of the send/receive buffers of MPI routines to the MPI\_Request object to distinguish among different types of communications (i.e., CPU versus GPU). Our proposed GPU-aware FPMPI library is capable of providing a separate profiling list for both the CPU and GPU MPI routines. The GPU-aware FPMPI is used to profile the GPU application in Chapter 6.

#### 2.2.3 GPU Advanced Features

In this section, we review some of the state-of-the-art features that exist in the latest generations of the NVIDIA GPUs.

GPU Inter-process communications Modern NVIDIA GPUs provide data copy mechanisms that can facilitate and improve the GPU inter-process communications. In this regard NVIDIA introduced CUDA Inter-Process Copy (IPC) and GPUDirect Remote Direct Memory Access (RDMA) technology for intranode and internode GPU inter-process communications.

With The NVIDIA CUDA IPC, data can be directly copied (without host intervention) from the GPU address space of one process to the GPU address space of another process within the same root complex on the node. The CUDA IPC copy requires a process to expose a portion of its address space to the remote processes. In this regard, a memory handle of the shared address is created and passed to the remote processes. The remote processes can then access and modify the shared remote address space; however, synchronization between the involved processes is required to guarantee the completion of the copy. This synchronization is performed using a

shared CUDA IPC event, by one process recording it after initiating its IPC copy and the other process querying its completion.

GPUDirect RDMA is a capability that enables GPUs on different nodes to directly exchange data without needing to go through the CPU/system memory. This feature is introduced in the NVIDIA Kepler-class and allows third party devices such as InfiniBand (IB) [32] adapters to directly access memory on multiple GPUs within the same system but on different nodes, thus allowing them to directly communicate with each other. None of the proposed techniques in this dissertation rely on this feature.

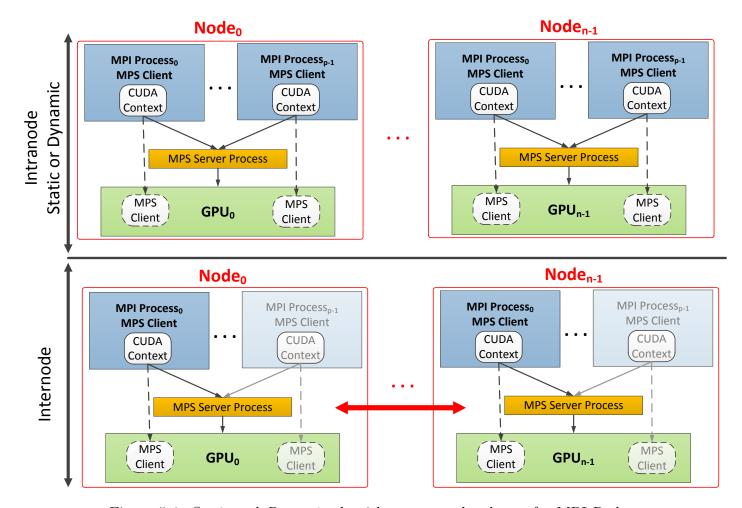

Hyper-Q and Multi Process Service: Hyper-Q [62] is an NVIDIA feature that provides potential concurrency among CUDA tasks from a single process. However, Hyper-Q by itself cannot provide concurrency among CUDA requests from multiple processes to the GPU compute and memory engine, thus these tasks would have to serialize. In order to provide such concurrency across multiple processes, NVIDIA has introduced the Multi Process Service (MPS) [64] for GPUs with compute capability of 3.5 and above. The MPS service acts as a funnel to collect CUDA tasks from multiple intranode processes and issue them to the GPU as if coming from a single process so that the Hyper-Q feature can take effect. Without this service, each of the MPI processes has to allocate storage and scheduling resources on the GPU, and only work from a single context can be launched on the GPU engines at a time. In contrast, with the MPS service enabled, there is only a single context, known as MPS context, present on the GPU. This allows all processes to share the GPU storage and scheduling resources, eliminating the overhead of the context switching. This feature is used in Chapter 5 to enhance the overlap between different GPU data copy mechanisms used in GPU collective communications.

Unified Virtual Addressing (UVA) UVA is an NVIDIA feature which has become available after CUDA 4.0. It maps GPU buffers into a single virtual address space and provides an aggregated virtual address space that is shared among the CPUs and the GPUs in the node. We use this feature in Chapter 3 to 6 to distinguish the GPU and CPU physical memory locations based on the buffer address value.

Unified Memory (UM) NVIDIA UM was introduced with CUDA 6. It creates a pool of managed memory that is shared between the CPU and GPU. With this feature the system automatically migrates data allocated in unified memory between host and device. This feature would allow codes running on the CPU and GPU to seamlessly use the system CPU and GPU memories. This feature eases hybrid programming and is not used in this dissertation.

# 2.3 Message Passing Interface (MPI)

The Message Passing Interface (MPI) [56] is a message-passing library which is considered as the de-facto standard programming model in HPC clusters. MPI has mainly gained interest due to its high performance, scalability, and portability. MPI has resulted from a joint effort of numerous groups and individuals starting in 1992. The first version of MPI standard (i.e, MPI-1.0) was released in 1994; The second MPI standard, MPI-2, was completed in 1998. MPI-3 was approved in 2012, and the latest available version of the MPI standard was released in 2015 (i.e., MPI-3.1). In the rest of this section, we first overview the message passing communication subsystem. Next, we introduce various MPI communication models and specifically overview the well-known algorithms that are typically used with the collective communication model. In this section, we also overview the current GPU support of some of the

well-known MPI libraries.

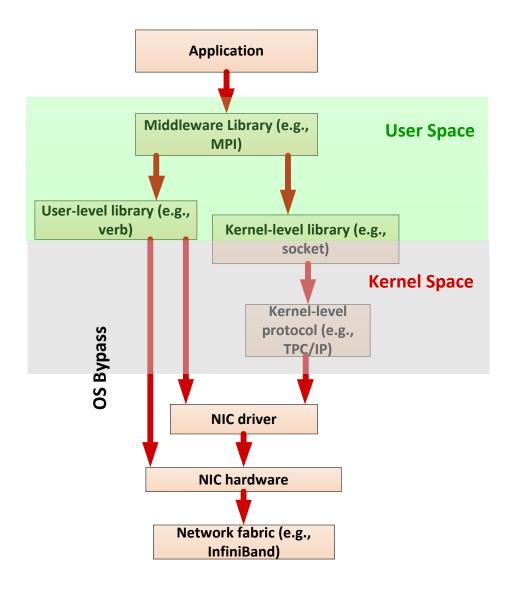

#### 2.3.1 Message Passing Communication Subsystem

Fig. 2.1 shows different levels of the message passing subsystem architecture. The application is at the highest level. Below the application level is the middleware library level; the MPI routines are exposed to the application developer at this level. The middleware library sits on top of the kernel-level or the user-level communication libraries. Both the middleware and the user-level libraries are directly accessible by the user and do not require any OS kernel intervention. At the kernel communication level, libraries, such as socket, interact with the kernel-level network protocols (such as TCP/IP); the kernel-level interfaces the kernel-level library with the Network Interface Card (NIC) driver. The user-level library, on the other hand, provides communication libraries that can bypass the OS; communications through this layer decreases the processing overhead between the middleware library and the NIC. As an example, the user level verb library allows MPI to interface to the Mellanox Infini-Band NIC driver or directly to the NIC hardware. The NIC hardware is connected to the network fabric (such as InfiniBand), which connects the node to the rest of the computer cluster. Our proposals in this dissertation are applied in the middleware library and we also utilize some functions from the user-level library.

#### 2.3.2 MPI Communication Models

In MPI, processes pass messages to each other in a cooperative fashion; this is known as the classical point-to-point communication model. MPI also provides an extension to this model for collective and Remote Memory Access (RMA) operations, we discuss

Figure 2.1: Message passing communication diagram

these communication models in more detail below.

Point-to-point: In MPI point-to-point communication, both sender and receiver take part in the communication. The sender calls a send routine, such as MPI\_Send(), and the receiver calls a receive routine such as MPI\_Recv(), both providing matching operations in order to recognize and select the right message. MPI point-to-point

communication comes in two flavors: 1) blocking and 2) non-blocking. The sender and receiver can either be blocking or non-blocking. The blocking sender blocks the calling process until it is safe to reuse the send buffer again; the blocking receiver blocks the receiver process until the receive operation is complete. In non-blocking send, the send operation will return as soon as the data is copied into the send communication buffer; non-blocking receive returns as soon as the receive request is posted. Non-blocking operations require polling or waiting to verify the completion of the message.

Collectives: MPI also supports collective communication operations which involves communications among two or more processes. Collective communications simplifies programming parallel applications, and facilitates implementation of efficient communication on various machines; this would in turn promote the portability of the application. The performance of different collective operations with different configurations, such as message size and process count, highly rely on the algorithm used to implement them [76, 10, 90].

Prior to MPI-3 all of the collective operations were blocking. Non-blocking collectives, first introduced in the MPI-3, are used to optimize collective communication by enabling overlap between communication and computation. In the blocking collective, the caller is blocked until it is safe to use the buffer it passed to the collective operation; while, in the non-blocking version, the call returns immediately which can be queried later to check its completion.

MPI collectives, in general, can be categorized as computational, synchronization, and data movement routines. In computational collectives, a group of processes work together to perform computations on a dataset that is distributed among them. For example, MPI\_Reduce performs a reduction operation (such as addition) on a dataset that is distributed among processes and stores the result in the root process. MPI\_Allreduce is another example of the computational collectives in which a reduction operation is performed on a distributed dataset, and the result is gathered by all processes.

The only operation in the synchronization category is MPI\_Barrier which also comes in a non-blocking format (i.e., MPI\_Ibarrier). This routine is considered to be complete once all of the processes have called it. Collective operations for data movement have two types. The first type distributes/stores the result from/into one process known as root (e.g., MPI\_Bcast and MPI\_Gather); the second type stores the final result in all of the processes (e.g., MPI\_Allgather); another collective operation in this type is MPI\_Alltoall in which each process sends a different chunk of data to each of the other processes. Neighborhood and Non-blocking collectives are the newly added collective operations in the MPI-3 standard [56].

Neighborhood collectives are introduced in MPI-3 standard [56] for the high demand of applications with sparse communication patterns (e.g., applications with stencil kernels). Before MPI-3, it was possible to use MPI process topology to create process topology graph, however, no communication function was introduced to utilize them. Neighborhood collectives enable collective operations to perform computation along the edges of the process topology.

RMA: In an RMA operation, a process is involved in a one-sided communication, specifying communication parameters for both sending and receiving sides. One side of the communication can directly read or write from/into an exposed memory window of the other side. MPI-2 RMA was strictly devised for limited application behavior patterns, and it had many missing features. MPI-3 addresses some of these shortcomings and supports broader application domain by optimizing window creation, memory model, and the synchronization methods. In this dissertation, we do not consider MPI RMA operations and mainly target collective communication routines.

MPI Libraries: Today, various MPI implementations are available; some are proprietary and some are open source. Intel-MPI [35] is an example of a proprietary implementation, while MPICH [57], MVAPICH [59], and Open MPI [68] are three of the open source implementations of the MPI library. MPICH is a widely portable implementation of the MPI standard that is maintained by the Argonne National Laboratory. MPICH3 is the base source code for many other open source and proprietary implementations that target specific interconnection networks. MVAPICH/MVAPICH2 is an example of such implementations, which is maintained by the Ohio State University and is optimized for using InfiniBand [32], Omni-Path [19], iWARP [78], and RoCE [5] networking technologies. Open MPI is also an open source implementation of the MPI standard that is maintained by a consortium of academic, research, and industry partners. It combines several features from different MPI implementations and has widespread use due to its high community support. We utilize MVAPICH2 library in Chapter 3 and 4; we use both MVAPICH2 and MVAPICH2-GDR libraries in Chapter 5; in Chapter 6, Open MPI library is used.

#### 2.3.3 MPI Collective Communication Algorithms

Collective communications are important and highly used component of MPI [76]. In HPC applications, there are stages of local computation followed by global communication. Programming such global communications can be simplified by using MPI collective operations. Efficient implementation of such operations on one hand removes this burden from the programmer and also promotes the portability of the application to different machines. In this regard, various algorithms have been proposed for different configurations of collective operations. Below, we overview some of the well-known collective algorithms.

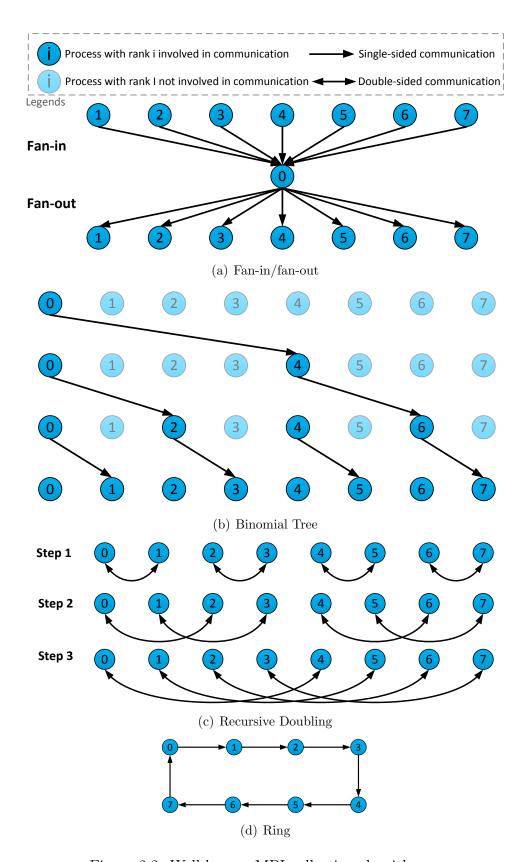

Fan-in/fan-out: In the fan-in algorithm [28] with radix-n, a single process, the parent process, serially receives data from n other processes; this algorithm can be used in collective operations such as MPI\_reduce and MPI\_gather. In the fan-out algorithm with radix-m, the parent process informs processes that data is ready and m processes can attempt to simultaneously read this data; this algorithm can be used in collective operations such as MPI\_Scatter and MPI\_Bcast. The fan-in and fan-out operations can be combined together and used in collective operations such as MPI\_Allreduce. The fan-in/fan-out algorithm is useful when synchronization cost among participating processes in the collective operation is costly. Fig. 2.2.(a) shows the general steps of the radix-7 fan-in/fan-out algorithm.

Binomial Tree: The steps of the binomial tree algorithm [90] are shown in Fig. 2.2.(b). In the first step, the root process sends data to process root + P/2 with P being the total number of processes; in the next step, both this and the root process act as new roots in their own subtrees and algorithm continues recursively. This communication takes a total of log(P) steps. The binomial tree algorithm can be used in various collective operations such as broadcast, gather, and reduce. However,

this algorithm is traditionally favored for short message sizes in flat systems.

Recursive Doubling: Fig. 2.2.(c) shows the steps of the recursive doubling algorithm [90]. In the first step, processes that are a distance 1 apart exchange their data. In the second and third step, processes that are distance 2 and 4 apart exchange their data, respectively. For P number of processes, recursive doubling ends in log(P) steps. Recursive doubling works well for power-of-two number of processes, while it is tricky to use it with non-power-of-two number of processes. Recursive Doubling is used in MPI collectives such as MPI\_Allgather and MPI\_Allreduce. In MPI\_Allreduce, however, each process also performs a local reduction on the exchanged data in each step. Recursive doubling is usually avoided when large messages are involved and other algorithms, such as the ring algorithm, are used [76].

Rabenseifner: The Rabenseifner algorithm [76] implements MPI\_Reduce as reduce-scatter followed by a gather to the root. At each reduce-scatter step, each process works on reducing a portion of the data. A gather operation (or allgather in case of MPI\_Allreduce) is called to collect the reduction results into the root.

Ring: In the ring algorithm [90], each process sends its data around a virtual ring of processes. As shown in Fig. 2.2.(d), in each step process i sends its contribution to process i + 1 and receives the contribution from process i - 1 (with wrap-around). In each step of this algorithm, each process sends the data it received in the previous step. With P processes, the ring algorithm takes P - 1 steps to complete. The ring algorithm is used in MPI collective operations such as MPI\_Allgather. It is showed, however, to only work efficiently on collectives with large message sizes.

Figure 2.2: Well-known MPI collective algorithms

#### 2.3.4 GPU-Aware MPI

There are many MPI applications that are written from scratch or have been adapted to run on the GPU clusters. In such clusters, the compute-intensive portion of the application is offloaded and accelerated on the GPU. In such applications, MPI processes are required to communicate the data that is residing on the GPU buffers. The GPU-aware MPI can remove the burden of learning a new programming language from the programmer to use MPI efficiently in conjunction with the GPU. The GPU-aware MPI would help the programmer to develop a more concise, readable and even efficient application to run on the GPU clusters.

In this regard, the GPU support has been added to the well-known MPI implementations such as MVAPICH2 [59] and Open MPI [68] in order to facilitate the data movement between MPI process from/to the GPU buffers. The GPU support in MPI libraries may follow a general approach which involves staging the GPU data into the host buffer and leveraging the CPU-based MPI routines. It may also involve further tunings by pipelining the transfers and using specifically designed algorithms for some MPI routines. The first step in the general approach involves copying the pertinent data from the GPU global memory into their host memory buffers; next, MPI operation is performed on data that resides on the host buffers, and finally the result is written back to the GPU memory. Depending on the message size, some MPI implementations such as MVAPICH2 may leverage a host-based pipelining design to hide the CUDA memory copy latency or use a more advanced design such as, Fine Grained Pipeline (FGP) algorithm [84] that is proposed for MPI\_Allgather. The FGP algorithm exploits simultaneous asynchronous network transfers and CUDA copies in a store and forward fashion.

MVAPICH2-GDR 2.0 is a proprietary design of the MPI standard that leverages the GPUDirect RDMA technology to achieve significant improvement for small message GPU-to-GPU communication. MVAPICH2-GDR takes advantage of the loopback and gdrcopy features in the intranode point-to-point and collective operations for small messages. The loopback design replaces the CUDA memory copy that has an initial calling overhead that is not negligible for short messages; the loopback design provides a virtual network interface allowing the node to communicate with itself. The GDR copy has a non-blocking nature, allowing the transfer to progress in parallel and thus incurring a lower latency compared to the CUDA memory copy used in MVAPICH2.

Current GPU-aware collective operations neither utilize efficient GPU-aware algorithms, nor fully exploit modern GPU features. Moreover, while different data copy mechanisms have been proposed for GPU inter-process communications, efficiently leveraging them in collective operations has not been investigated. The existing GPU-aware collective operations leverage flat designs which are inefficient given the hierarchical structure of many multi-GPU nodes and GPU clusters.

#### 2.4 Modern Interconnects and Communication Channels

GPU inter-process communication plays a crucial role in the performance of the applications running on the GPU clusters. GPU inter-process communications can happen within a single node (known as intranode communication), or across the network (known as internode communication). Both intranode and internode communications have been shown to considerably affect the performance of the applications running on the GPU clusters [70]. In this regard, several high-speed interconnection networks

and communication channels are used to interconnect GPUs within and across the nodes.

According to the Top500 [91], various interconnection networks can be used to interconnect HPC clusters with GPU accelerators, such as InfiniBand [32], Aries [19], Omni-Path [7], 10G Ethernet, and other proprietary interconnects. Among these interconnection networks, InfiniBand has the highest share among the top 500 supercomputers with GPU accelerators [91].

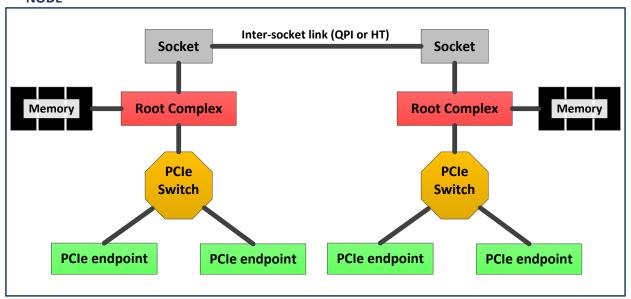

Today, a common practice with many of the GPU clusters is to use multi-GPU nodes to increase their computation power and bandwidth capacity. Inter-process communications within these nodes can go through different communication channels such as PCIe tree topology, NVLink connection [66], and inter-socket links.