# SCALABILITY-DRIVEN APPROACHES TO KEY ASPECTS OF THE MESSAGE PASSING INTERFACE FOR NEXT GENERATION SUPERCOMPUTING

by

#### AYI JUDICAEL ZOUNMEVO

A thesis submitted to the Department of Electrical and Computer Engineering in conformity with the requirements for the degree of Doctor of Philosophy

Queen's University Kingston, Ontario, Canada May 2014

Copyright © Ayi Judicael Zounmevo, 2014

### Abstract

The Message Passing Interface (MPI), which dominates the supercomputing programming environment, is used to orchestrate and fulfill communication in High Performance Computing (HPC). How far HPC programs can scale depends in large part on the ability to achieve fast communication; and to overlap communication with computation or communication with communication.

This dissertation proposes a new asynchronous solution to the nonblocking Rendezvous protocol used between pairs of processes to transfer large payloads. On top of enforcing communication/computation overlapping in a comprehensive way, the proposal trumps existing network device-agnostic asynchronous solutions by being memory-scalable and by avoiding brute force strategies.

Achieving overlapping between communication and computation is important; but each communication is also expected to generate minimal latency. In that respect, the processing of the queues meant to hold messages pending reception inside the MPI middleware is expected to be fast. Currently though, that processing slows down when program scales grow. This research presents a novel scalability-driven message queue whose processing skips altogether large portions of queue items that are deterministically guaranteed to lead to unfruitful searches. For having little sensitivity to program sizes, the proposed message queue maintains a very good performance, on top of displaying a low and flattening memory footprint growth pattern.

Due to the blocking nature of its required synchronizations, the one-sided communication model of MPI creates both communication/computation and communication/communication serializations. This research fixes these issues and latency-related inefficiencies documented

for MPI one-sided communications by proposing completely nonblocking and non-serializing versions for those synchronizations. The improvements, meant for consideration in a future MPI standard, also allow new classes of programs to be more efficiently expressed in MPI.

Finally, a persistent distributed service is designed over MPI to show its impacts at large scales beyond communication-only activities. MPI is analyzed in situations of resource exhaustion, partial failure and heavy use of internal objects for communicating and non-communicating routines. Important scalability issues are revealed and solution approaches are put forth.

# Acknowledgments

Thanks to God for past and current graces, for the wisdom he offers for free; and for watching over me and my future.

I am deeply indebted to my supervisor, Dr. Ahmad Afsahi, for his unfailing support and for constantly pushing me toward the completion of this research. My thanks go to him for his guidance for high quality research, understanding and praiseworthy patience. I am also indebted to Dr. Dries Kimpe, Dr. Pavan Balaji and Dr. Rob Ross of the U.S. Argonne National Laboratory, IL. I undeniably grew with their advice and insight during my Ph.D. studies. To the members of my thesis committee, Dr. Ying Zou, Dr. Ahmed Hassan, Dr. Michael Korenberg and Dr. Jesper Larsson Träff, thanks for the priceless feedback on this research.

To my co-workers from the Parallel Processing Research lab, Dr. Ying Qian, Dr. Mohammad Rashti, Dr. Ryan Grant, Dr. Reza Zamani, Grigory Inozemtsev, Iman Faraji and Hessam Mirsadeghi, thanks for your support, the constructive discussions, the jokes and the laughters. The experience would have been lonely without you. To Ryan, additional thanks for those spontaneous and extremely helpful advice in my last year. To Iman and Hessam, thanks for now being two irreplaceable friends for life. Thanks to Xin Zhao of the University of Illinois Urbana Champaign for the collaboration and insightful discussions on MPI one-sided communications.

Thanks to the Natural Science and Engineering Research Council of Canada (NSERC) for supporting this research through grants to my supervisor. Thanks to the Electrical and Computer Engineering (ECE) Department of Queen's University as well as the school of graduate studies for the financial support. Thanks to the IT service and office staff of the ECE

Department of Queen's University. Special thanks to Ms. Debra Fraser and Ms. Kendra Pople-Easton for being so nice, so supportive and so available for me. My gratitude also goes to Pak Lui and the HPC Advisory Council for the supercomputing resources. Thanks to the Argonne Laboratory Computing Research Center for the supercomputing resources.

To all my friends in Montreal, I cannot acknowledge enough your support. In alphabetical order, Narcisse Adjalla, Santos Adjalla, Sami Abike Yacoubou-Chabi Yo, Sani Chabi Yo, Florent Kpodjedo, Ablan Joyce Nouaho and Fatou Tao, thank you. As for Florent, my improvised psychologist in difficult and lonely moments, additional thanks; you actually watched over me.

Lastly, I would like to acknowledge my family for always believing in me. My gratitude goes to my brothers and sisters, Ida, Cyr, Hervé, Eric, Lydia, Annick and Laure for their support and prayers. To my father Fabien and my mother Jeanne, you are the absolute mental strength that I carry with myself; I owe you so much.

# Table of Contents

| Abstra  | act                                                             | i                      |

|---------|-----------------------------------------------------------------|------------------------|

| Ackno   | owledgments                                                     | iii                    |

| Table   | of Contents                                                     | v                      |

| List of | f Tables                                                        | ix                     |

| List of | f Figures                                                       | x                      |

| List of | f Equations                                                     | xiii                   |

| List of | f Code Listings                                                 | xiv                    |

| Acron   | yms                                                             | $\mathbf{x}\mathbf{v}$ |

| Chapt   | er 1:                                                           |                        |

|         | Introduction                                                    | 1                      |

| 1.1     | Motivation                                                      | 3                      |

| 1.2     | Problem Statement                                               | 7                      |

| 1.3     | Contributions                                                   | 8                      |

| 1.4     | Dissertation Outline                                            | 11                     |

| Chapt   |                                                                 |                        |

|         | Background                                                      | 13                     |

| 2.1     | Message Passing Interface (MPI)                                 | 14                     |

|         | 2.1.1 Datatypes and Derived Datatypes in MPI                    | 16                     |

|         | 2.1.2 Two-sided Communications                                  | 17                     |

|         | 2.1.3 Collective Communications                                 | 19                     |

|         | 2.1.4 One-sided Communications                                  | 19                     |

|         | 2.1.5 The Nonblocking Communication Handling in MPI             | 23                     |

|         | 2.1.6 Generalized Requests and Info Objects                     | 24                     |

|         | 2.1.7 Thread Levels                                             | 25                     |

| 2.2     | High Performance Interconnects                                  | 26                     |

|         | 2.2.1 InfiniBand: Characteristics, Queueing Model and Semantics | 28                     |

|         | 2.2.2 The Lower-level Messaging Middleware                      | 29                     |

| 2.3     | Summary                                                         | 30                     |

| Chapte |                                                                             |

|--------|-----------------------------------------------------------------------------|

|        | Scalable MPI Two-Sided Message Progression over RDMA 31                     |

| 3.1    | Introduction to Rendezvous Protocols                                        |

|        | 3.1.1 RDMA Write-based Rendezvous Protocol                                  |

|        | 3.1.2 RDMA Read-based Rendezvous Protocol                                   |

|        | 3.1.3 Synthesis of the RDMA-based Protocols and Existing Improvement Pro-   |

|        | posals                                                                      |

|        | 3.1.4 Hardware-offloaded Two-sided Message Progression                      |

|        | 3.1.5 Host-based Asynchronous Message Progression Methods 41                |

|        | 3.1.6 Summary of Related Work                                               |

| 3.2    | Scenario-conscious Asynchronous Rendezvous                                  |

|        | 3.2.1 Design Objectives                                                     |

|        | 3.2.2 Asynchronous Execution Flows inside a Single Thread                   |

| 3.3    | Experimental Evaluation                                                     |

| 0.0    | 3.3.1 Microbenchmark Results                                                |

|        | 3.3.2 Application Results                                                   |

| 3.4    | Summary                                                                     |

| 0.1    |                                                                             |

| Chapte | er 4:                                                                       |

|        | Scalable Message Queues in MPI 60                                           |

| 4.1    | Related Work                                                                |

| 4.2    | Motivations                                                                 |

|        | 4.2.1 The Omnipresence of Message Queue Processing in MPI Communications 63 |

|        | 4.2.2 Performance and Scalability Concerns                                  |

|        | 4.2.3 Rethinking Message Queues for Scalability by Leveraging MPI's Very    |

|        | Characteristics                                                             |

| 4.3    | A New Message Queue for Large Scales                                        |

|        | 4.3.1 Reasoning about Dimensionality 69                                     |

|        | 4.3.2 A Scalable Multidimensional MPI Message Sub-queue                     |

|        | 4.3.3 Receive Match Ordering Enforcement                                    |

|        | 4.3.4 Size Threshold Heuristic for Sub-queue Structures                     |

| 4.4    | Performance Analysis                                                        |

|        | 4.4.1 Runtime Complexity Analysis                                           |

|        | 4.4.2 Memory Overhead Analysis                                              |

|        | 4.4.3 Cache Behaviour                                                       |

| 4.5    | Practical Justification of a New Message Queue Data Structure               |

| 4.6    | Experimental Evaluation                                                     |

| 1.0    | 4.6.1 Notes on Measurements                                                 |

|        | 4.6.2 Microbenchmark Results                                                |

|        | 4.6.3 Application Results                                                   |

|        | 4.6.4 Message Queue Memory Behaviours at Extreme Scales                     |

| 4.7    | Summary                                                                     |

| 7.1    | bullinary                                                                   |

| Chapte | er 5:                                                                       |

| •      | Nonblocking MPI One-sided Communication Synchronizations . 121              |

| 5.1    | Related Work                                                                |

| 5.2    | The Burden of Blocking RMA Synchronization                                  |

|                | 5.2.1 The Inefficiency Patterns                                             | 124  |

|----------------|-----------------------------------------------------------------------------|------|

|                | 5.2.2 Serializations in MPI One-sided Communications                        | 126  |

| 5.3            | Opportunistic Message Progression as Default Advantage for Nonblocking Syn- |      |

|                |                                                                             | 128  |

| 5.4            | Impacts of Nonblocking RMA Epochs                                           | 130  |

|                | 1                                                                           | 131  |

|                |                                                                             | 135  |

| 5.5            | • •                                                                         | 138  |

| 5.6            | 9                                                                           | 139  |

|                |                                                                             | 140  |

|                |                                                                             | 145  |

| 5.7            |                                                                             | 150  |

| · · ·          |                                                                             | 150  |

|                | 5.7.2 Deferred Epochs and Epoch Recording                                   |      |

|                | 1 0                                                                         | 153  |

|                | · · · · · · · · · · · · · · · · · · ·                                       | 155  |

| 5.8            |                                                                             | 156  |

| 0.0            | 1                                                                           | 157  |

|                |                                                                             | 176  |

|                | 5.8.3 Application Test                                                      |      |

| 5.9            | Summary                                                                     |      |

| 0.10           | ——————————————————————————————————————                                      |      |

| Chapte         | er 6:                                                                       |      |

|                | MPI in Extreme-scale Persistent Services: Some Missing Scala-               |      |

|                | bility Features                                                             | 186  |

| 6.1            | Related Work                                                                | 188  |

| 6.2            | Service Overview: The Distributed Storage                                   | 188  |

| 6.3            | Transport Requirements                                                      | 192  |

| 6.4            | MPI as a Network API                                                        | 193  |

|                | 1                                                                           | 194  |

|                | 6.4.2 The RPC Listener                                                      | 198  |

|                | 6.4.3 I/O Life Cycles                                                       | 199  |

|                | 6.4.4 Cancellation                                                          | 201  |

|                | 6.4.5 Client-server and Failure Behaviour                                   | 206  |

|                | 6.4.6 Object Limits                                                         | 209  |

| 6.5            | Some Missing Scalability Features                                           | 210  |

|                | 6.5.1 Fault Tolerance                                                       | 210  |

|                | 6.5.2 Generalization of Nonblocking Operations                              | 212  |

|                | 6.5.3 Object Limits and Resource Exhaustion                                 | 217  |

| 6.6            | Summary                                                                     | 218  |

| GI.            | _                                                                           |      |

| Chapte         |                                                                             | 04.7 |

| <del>-</del> - | Conclusion and Future Work                                                  |      |

| 7.1            | v G                                                                         | 220  |

| 7.2            | Future Work                                                                 | 224  |

| Diblios        | graphy                                                                      | 220  |

| List o | f Publications |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | . 2 | 40 | O |

|--------|----------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|----|---|

|--------|----------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|----|---|

# List of Tables

| 4.1  | Runtime complexity summary                                                                                                                | 88  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2  | Number of pointer operations required to reach the last queue item for different                                                          |     |

|      | communicator sizes (case of a single communicator)                                                                                        | 90  |

| 4.3  | Number of pointer operations required to reach the last queue item for different                                                          |     |

|      | communicator sizes (case of multiple communicators)                                                                                       | 90  |

| 4.4  | Runtime object sizes                                                                                                                      | 92  |

| 4.5  | Comparative memory overhead of the array-based approach and the 4D approach                                                               | 93  |

| 4.6  | Comparative speed test (in seconds) between the 4D design and a red-black tree                                                            |     |

|      | $\operatorname{design} \dots \dots$ | 97  |

| 4.7  | Memory overhead (in KB) of the 4D and red-black tree designs compared to the                                                              |     |

|      | linked list design (1 message per rank)                                                                                                   | 97  |

| 4.8  | PRQ behaviour data for Radix and Nbody                                                                                                    | .12 |

| 4.9  | UMQ behaviour data for Radix and Nbody                                                                                                    |     |

| 4.10 | Average memory overhead measurements of the applications (in KB) 1                                                                        | .17 |

| 4.11 | Memory consumption overhead extrapolation on Sequoia and Titan                                                                            | .19 |

| 6.1  | Behaviours in case of isolated server abortion                                                                                            | 207 |

| 6.2  | Storage job behaviours after client job failure                                                                                           | 30  |

| 6.3  | Object limits                                                                                                                             | 210 |

# List of Figures

| 2.1  | HPC cluster: Intra-node and out-of-node memory view                              |

|------|----------------------------------------------------------------------------------|

| 2.2  | HPC cluster: software stack view                                                 |

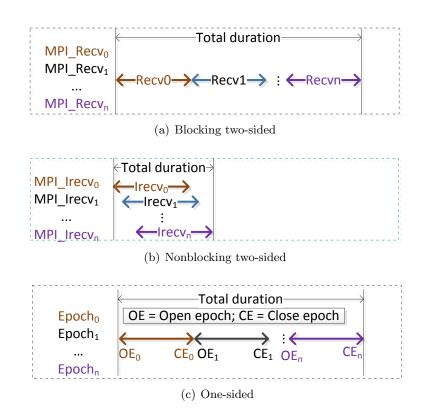

| 2.3  | Two-sided message transfer protocols                                             |

| 2.4  | MPI RMA synchronizations (inspired by [105])                                     |

| 2.5  | Zero-copy and CPU involvement (Adapted from [66])                                |

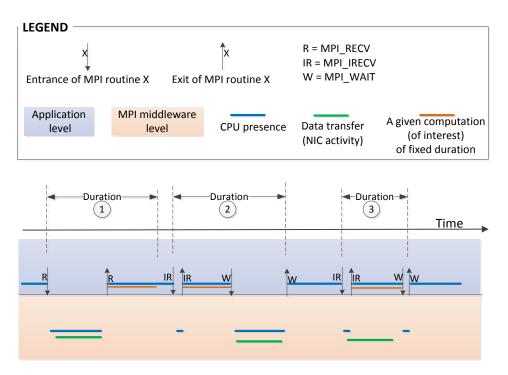

| 3.1  | Serialized and overlapped communication/computation                              |

| 3.2  | RDMA Write-based Rendezvous protocol                                             |

| 3.3  | RDMA Read-based Rendezvous protocol                                              |

| 3.4  | Receiver-initiated Rendezvous protocol                                           |

| 3.5  | Parasite execution flow-based message progression at receiver side for two-sided |

|      | communications                                                                   |

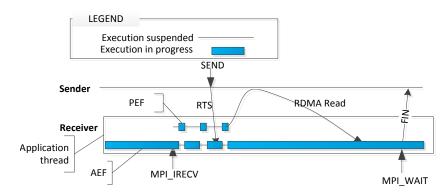

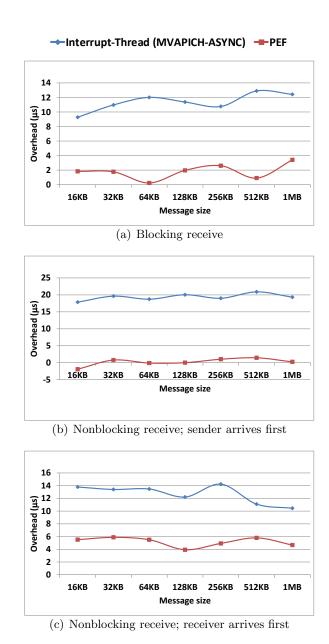

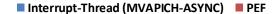

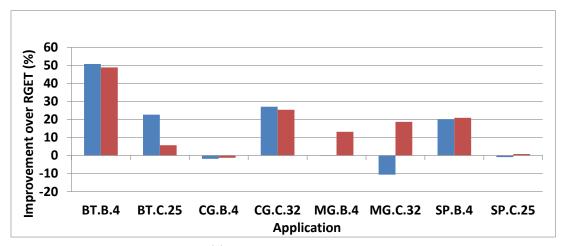

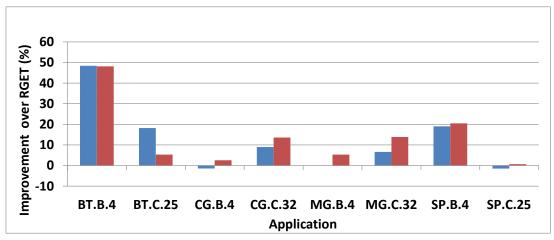

| 3.6  | Receiver-side latency overhead of interrupt-based threading (MVAPICH-ASYNC)      |

|      | vs. PEF. (RGET is the reference)                                                 |

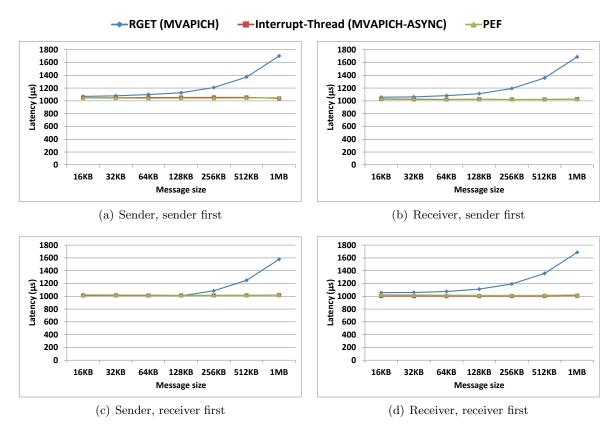

| 3.7  | Communication/computation overlapping of RGET (MVAPICH), interrupt-based         |

|      | threading (MVAPICH-ASYNC) and PEF                                                |

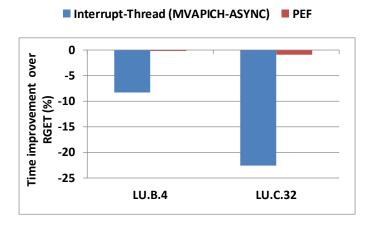

| 3.8  | Impact at receive side on the communication time of a job that resorts to block- |

|      | ing receives                                                                     |

| 3.9  | Nonblocking receive-based application benchmark results                          |

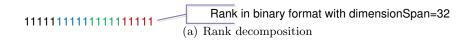

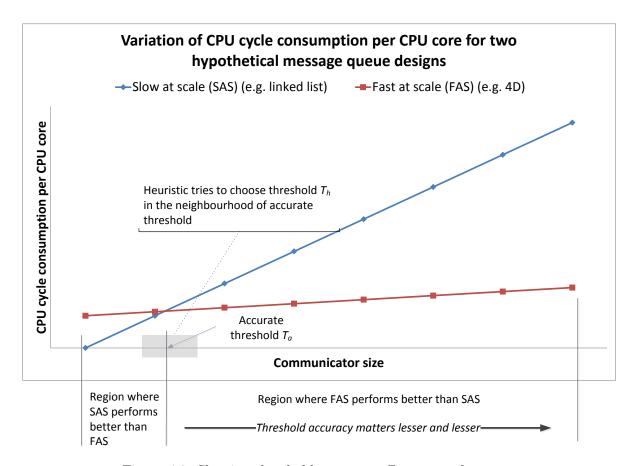

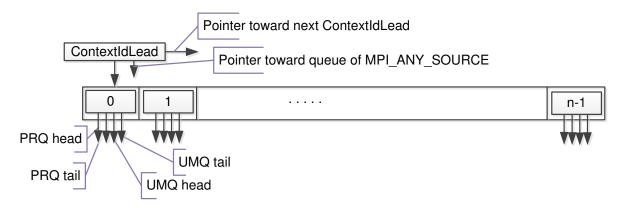

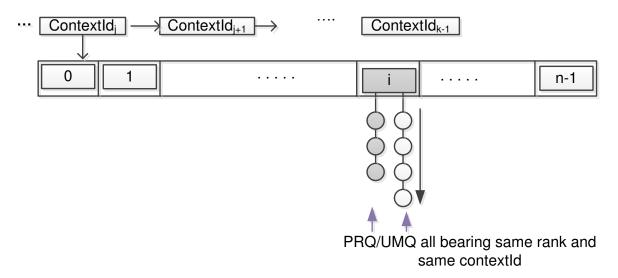

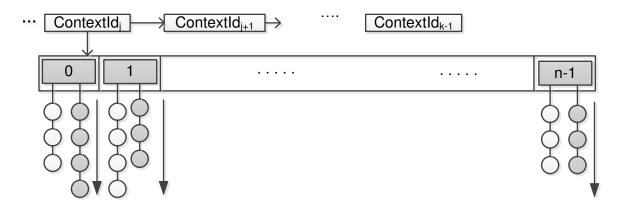

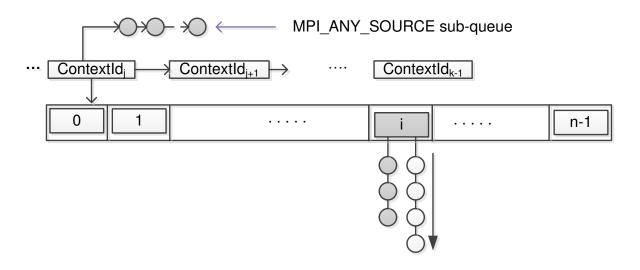

| 4.1  | 4-dimensional sub-queue with $dimensionSpan = 32 \dots \dots $ 75                |

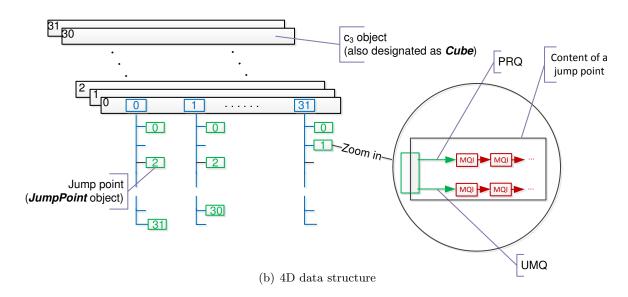

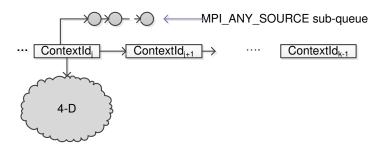

| 4.2  | New overall MPI message queue design                                             |

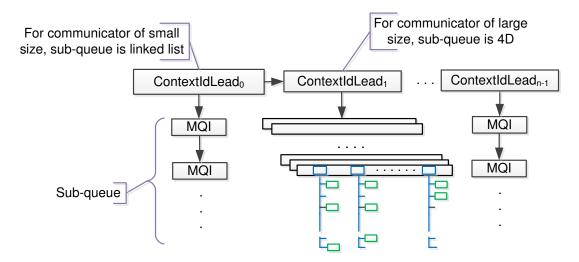

| 4.3  | Showing threshold accuracy effect on performance                                 |

| 4.4  | Array-based queue design for a communicator of size $n 	cdots$ . 81              |

| 4.5  | Array-based queue search in absence of MPI_ANY_SOURCE 83                         |

| 4.6  | Array-based UMQ search for MPI_ANY_SOURCE receive                                |

| 4.7  | Array-based PRQ search when at least one MPI_ANY_SOURCE receive is pending 84    |

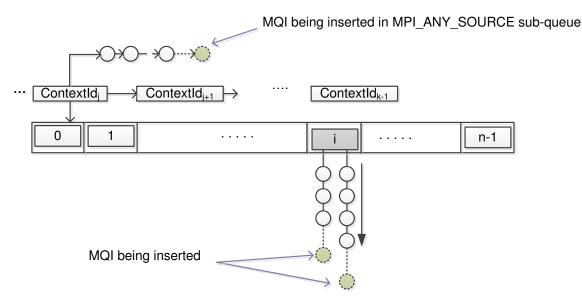

| 4.8  | Possible insertion points in the array-based structure                           |

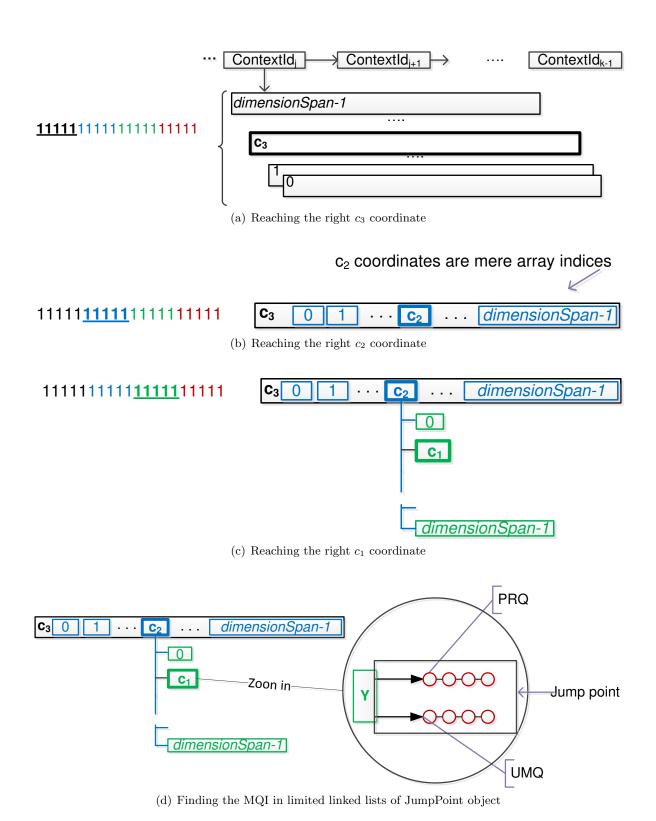

| 4.9  | 4D structure queue search in absence of MPI_ANY_SOURCE                           |

| 4.10 | 4D structure PRQ search in presence of MPI_ANY_SOURCE 8'                         |

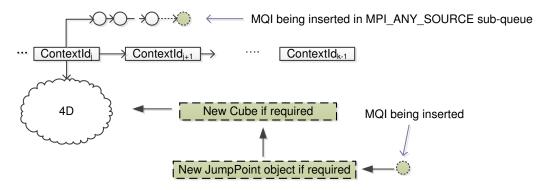

| 4.11 | Possible insertion points in the 4D structure                                    |

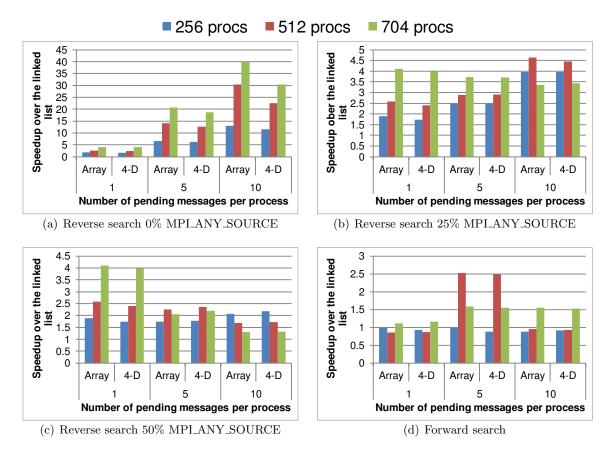

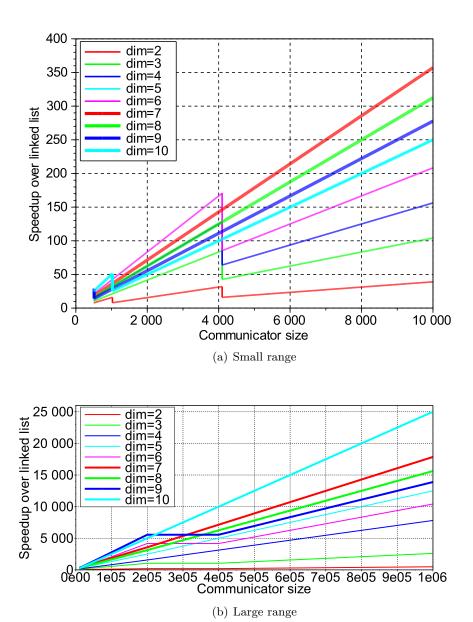

| 4.12 | PRQ operation speedup over the linked list, with 1 communicator 100              |

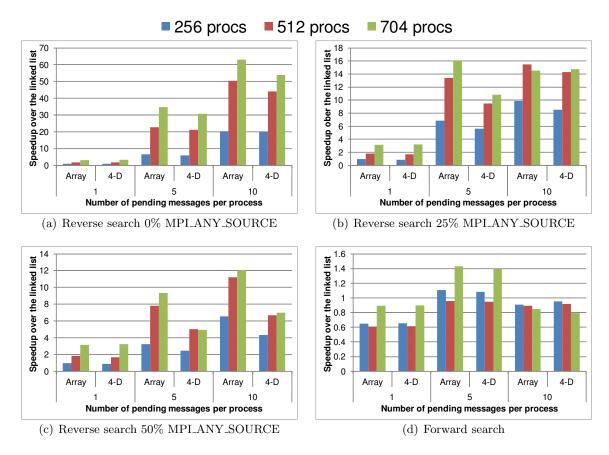

| 4.13 | UMQ operation speedup over the linked list, with 1 communicator 102              |

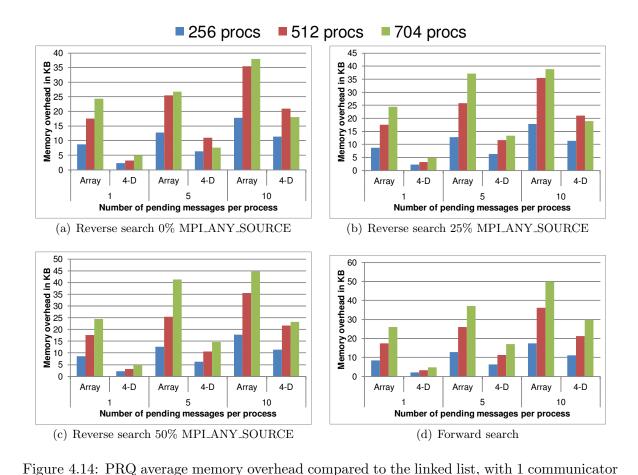

| 4.14 | PRQ average memory overhead compared to the linked list, with 1 communicator 103 |

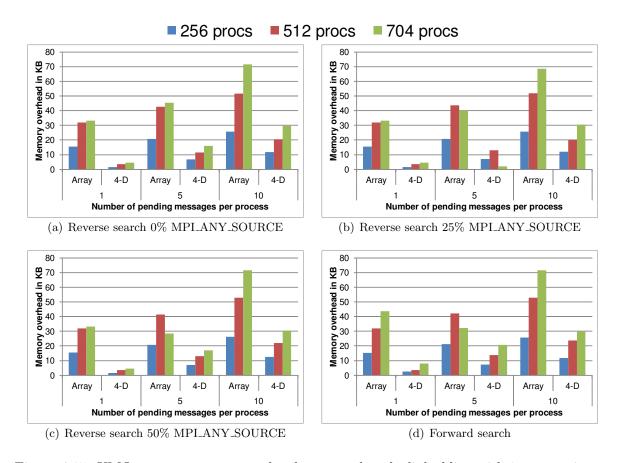

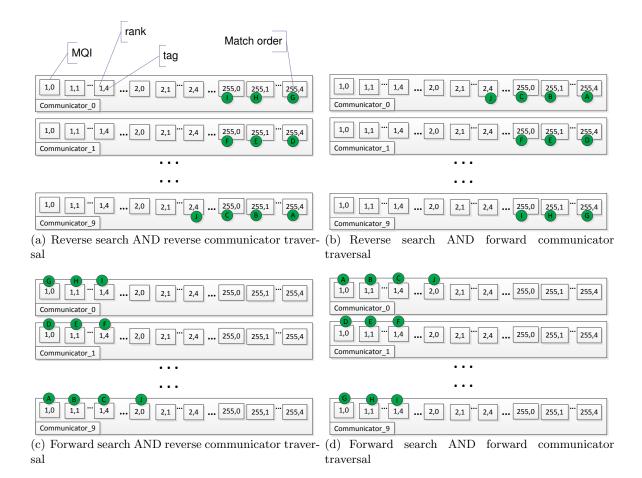

| 4.15 | UMQ average memory overhead compared to the linked list, with 1 communicator 10- |

| 4.16 | Different match orders for multi-communicator tests: example with 10 commu-      |

|      | nicators of 256 distinct ranks and 5 pending messages per process                |

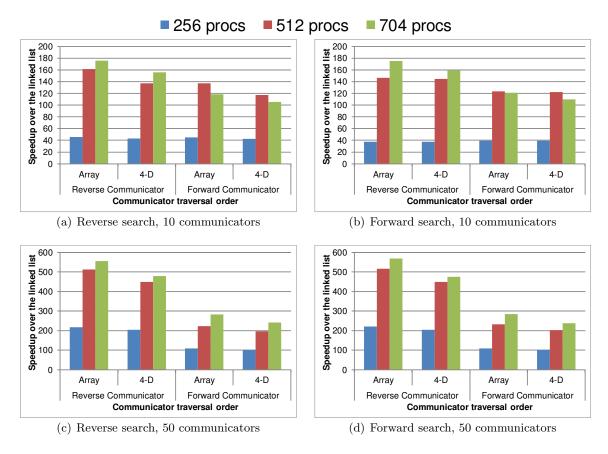

| 4.17 | PRQ operation speedup over the linked list, with multiple communicators 100      |

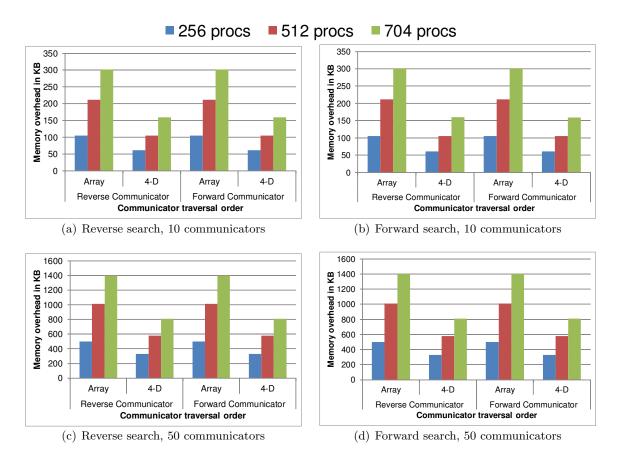

| 4.18 | PRQ average memory overhead compared to the linked list, with multiple com-            | 107  |

|------|----------------------------------------------------------------------------------------|------|

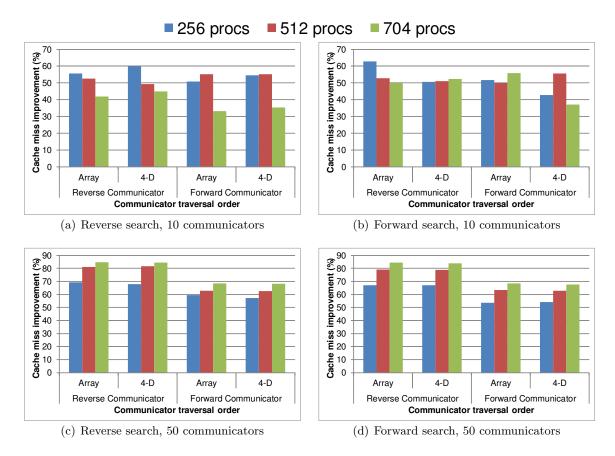

| 4.10 | municators                                                                             | 107  |

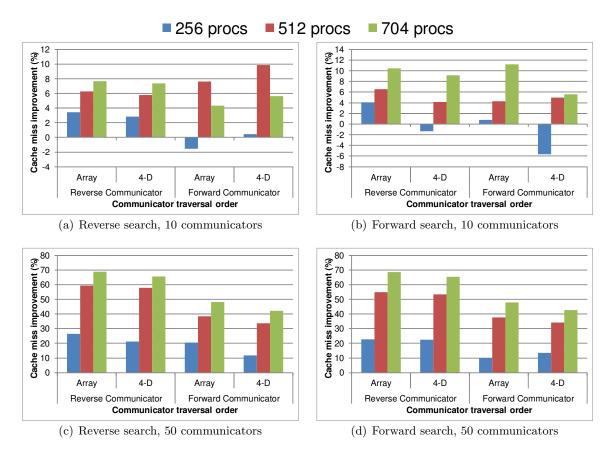

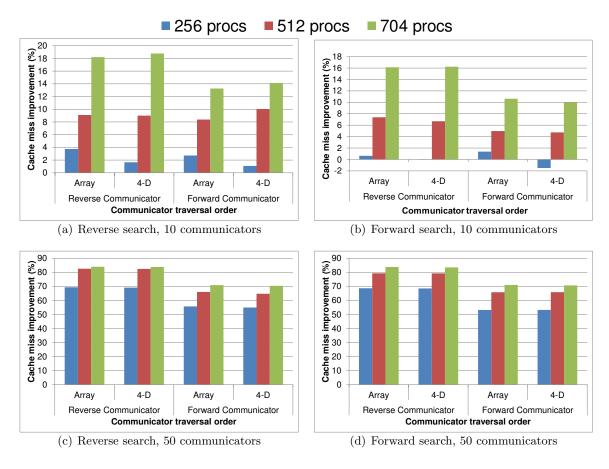

|      | PRQ L1 data cache improvement over the linked list, with multiple communicators        | 108  |

| 4.20 | PRQ L1 instruction cache improvement over the linked list, with multiple communicators | 109  |

| 1 91 | PRQ last level (L3) cache improvement over the linked list, with multiple com-         | 109  |

| 4.21 | municators                                                                             | 110  |

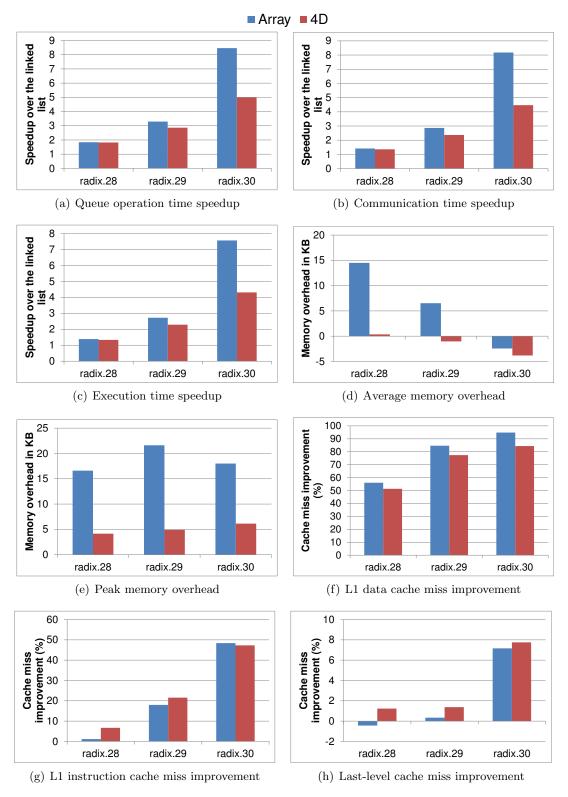

| 4 99 | Radix speedups, memory overhead and cache statistics for the array-based and           | 110  |

| 4.22 | 4D designs over the linked-list approach                                               | 113  |

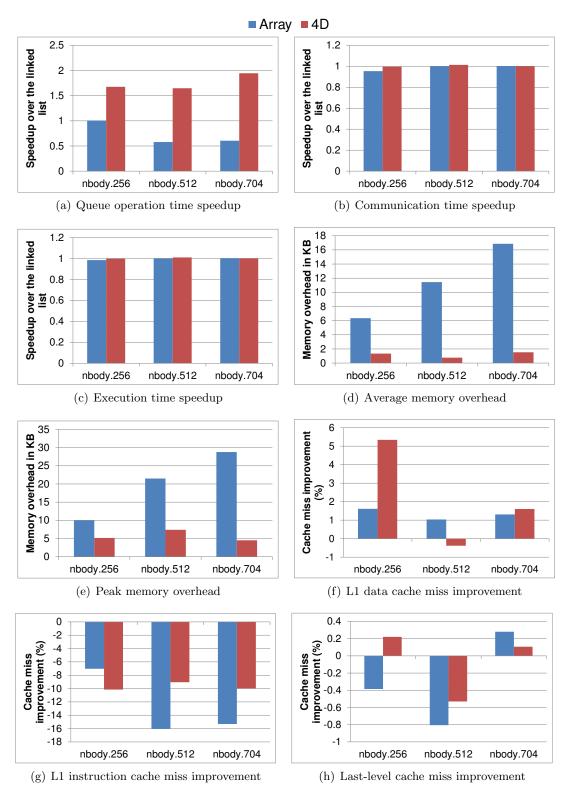

| 4 23 | Nbody speedups, memory overhead and cache statistics for the array-based and           | 110  |

| 1.20 | 4D designs over the linked-list approach                                               | 114  |

|      | 4D designs over the mixed list approach                                                | 111  |

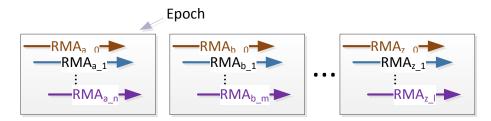

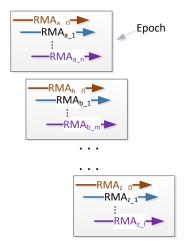

| 5.1  | Parallel RMA in serialized epochs                                                      | 127  |

| 5.2  | Serialized vs. non-serialized communications                                           | 127  |

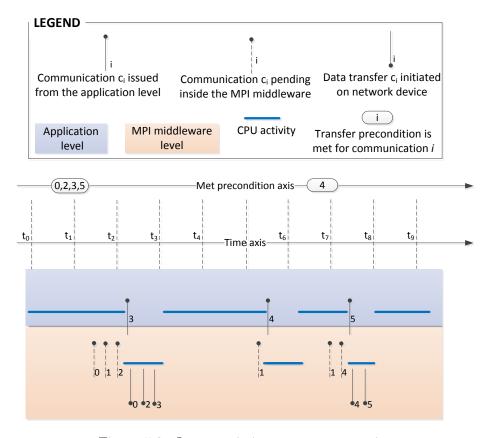

| 5.3  | Opportunistic message progression                                                      | 129  |

| 5.4  | Parallel epochs                                                                        | 130  |

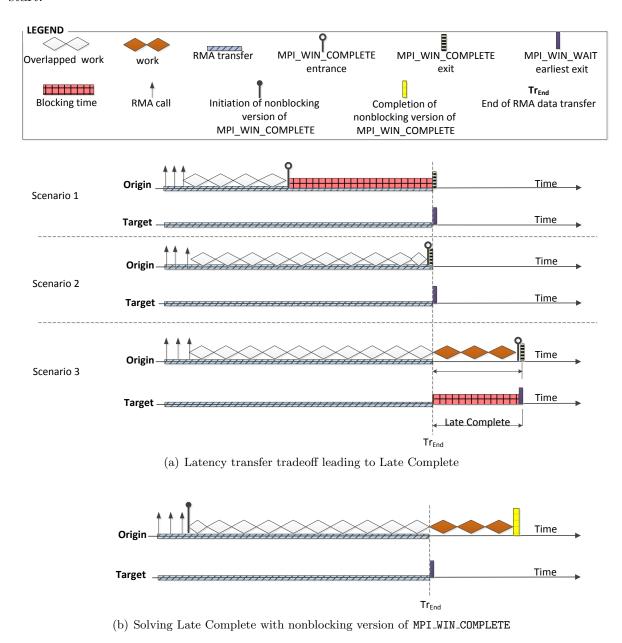

| 5.5  | Impact of nonblocking epochs on Late Complete                                          | 133  |

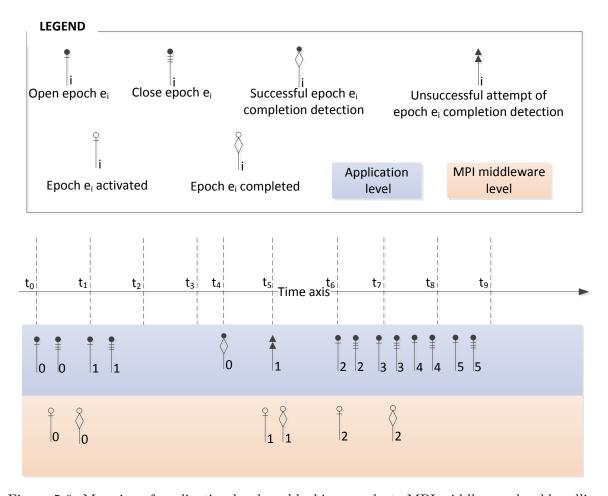

| 5.6  | Mapping of application-level nonblocking epochs to MPI middleware-level han-           |      |

|      | dling                                                                                  | 142  |

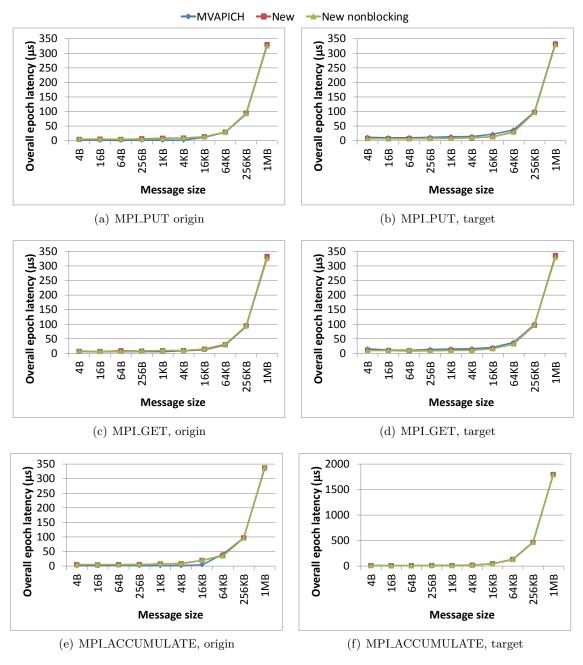

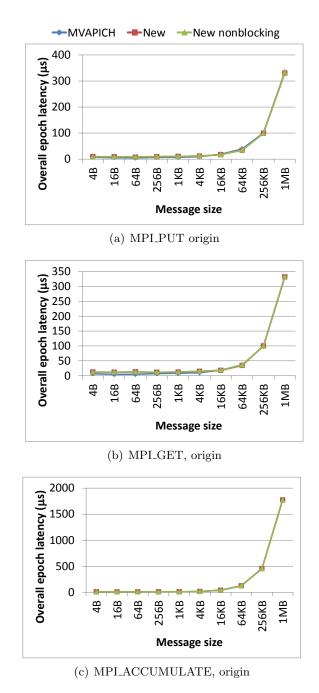

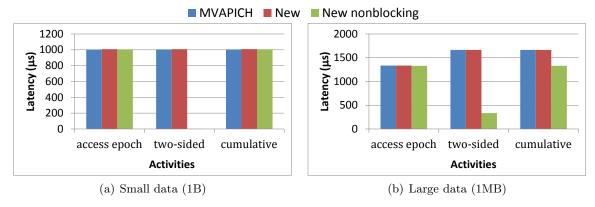

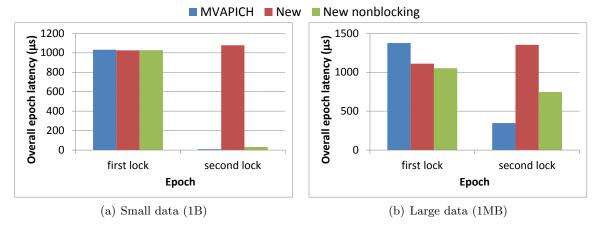

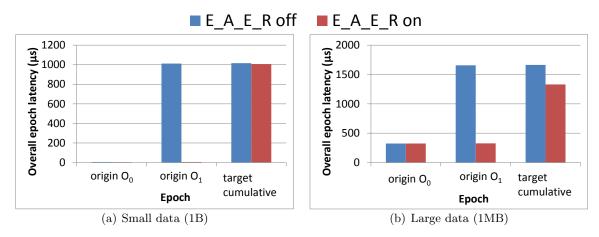

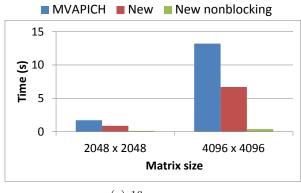

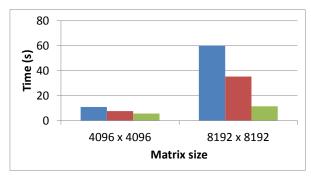

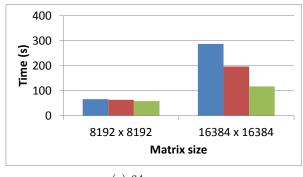

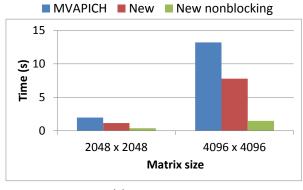

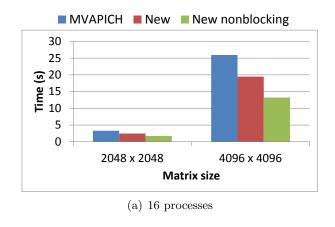

| 5.7  | Comparative overall GATS epoch latency of MVAPICH, blocking and nonblock-              |      |

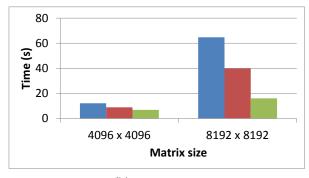

|      | ing versions of the new design                                                         | 159  |

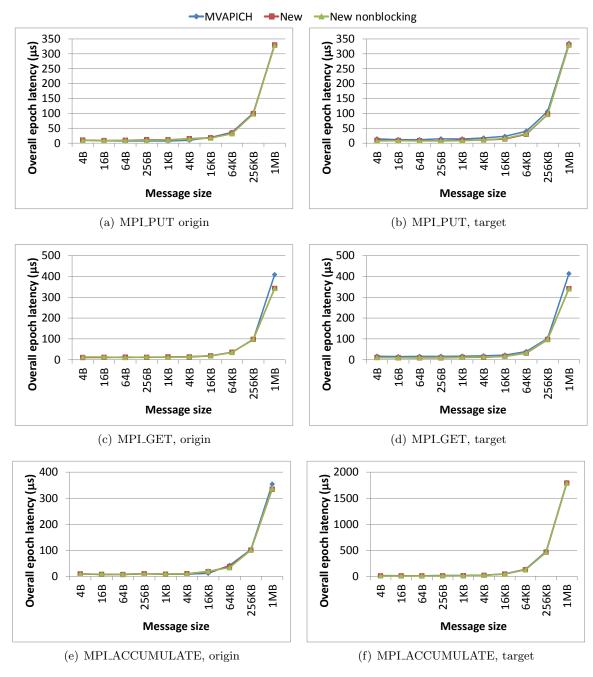

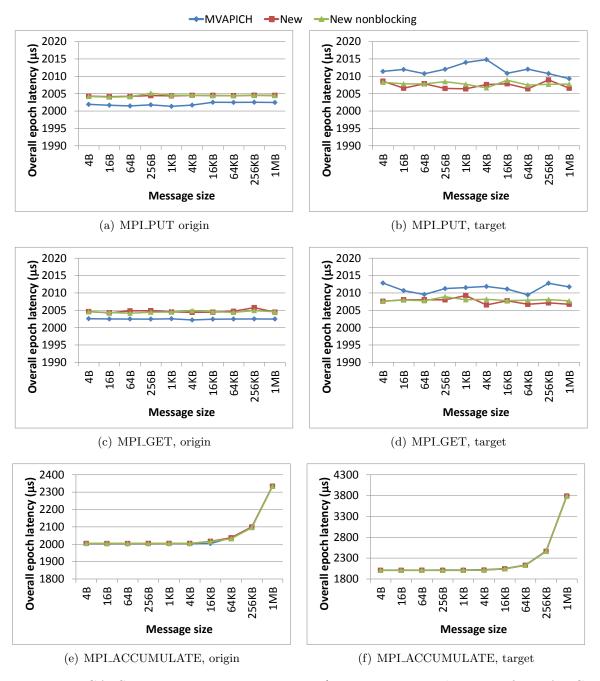

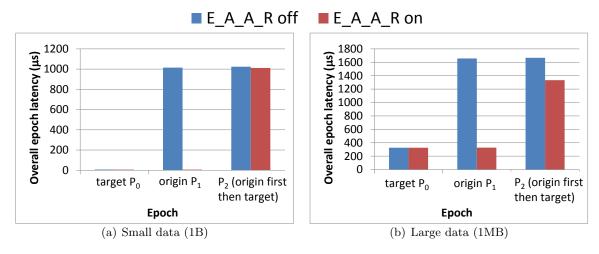

| 5.8  | Comparative overall fence epoch latency of MVAPICH, blocking and nonblock-             |      |

|      | ing versions of the new design                                                         | 160  |

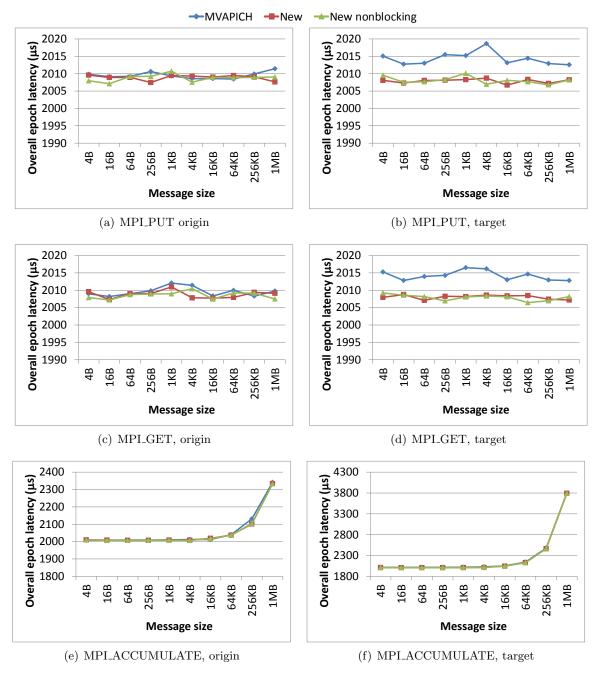

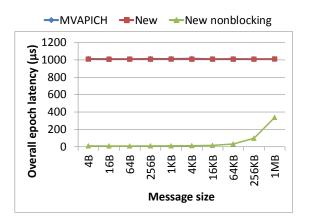

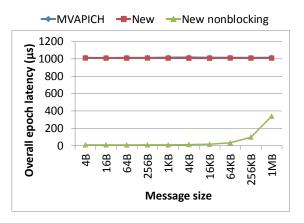

| 5.9  | Comparative overall lock epoch latency of MVAPICH, blocking and nonblocking            |      |

| - 10 | 9                                                                                      | 161  |

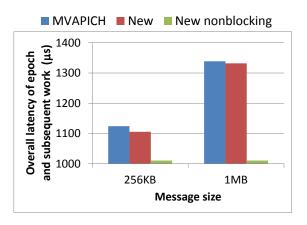

| 5.10 | GATS comparative communication/computation overlapping of MVAPICH, block-              |      |

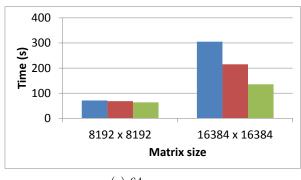

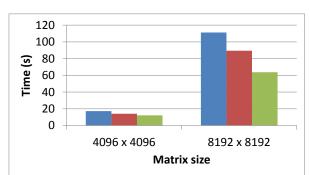

| F 11 |                                                                                        | 164  |

| 5.11 | Fence comparative communication/computation overlapping of MVAPICH, block-             | 165  |

| 5 19 | ing and nonblocking versions of the new design                                         | 165  |

| 5.12 | PICH, blocking and nonblocking versions of the new design                              | 166  |

| 5 12 | Mitigating the Late Post inefficiency pattern: observing delay propagation in          | 100  |

| 0.10 | an origin process                                                                      | 168  |

| 5 14 | Mitigating the Late Complete inefficiency pattern: observing delay propagation         | 100  |

| 0.11 | in a target process                                                                    | 169  |

| 5.15 | Mitigating the Early Fence inefficiency pattern: observing communication la-           | 100  |

| 0.20 | tency propagation in a target process                                                  | 170  |

| 5.16 | Mitigating the Wait at Fence inefficiency pattern: observing delay propagation         |      |

|      | in a target process                                                                    | 171  |

| 5.17 | Mitigating the Late Unlock inefficiency pattern: observing delay propagation to        |      |

|      | a subsequent lock requester                                                            | 172  |

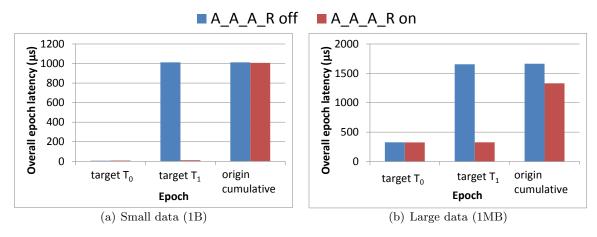

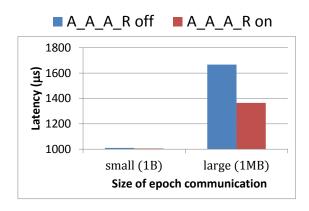

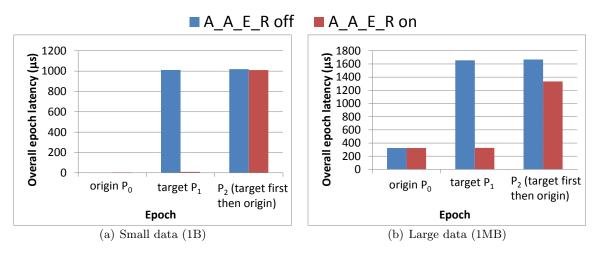

| 5.18 | Out-of-order GATS access epoch progression with MPI_WIN_ACCESS_AFTER_ACCESS            | 5_   |

|      | REORDER                                                                                | 174  |

| 5.19 | Out-of-order lock epoch progression with MPI_WIN_ACCESS_AFTER_ACCESS_REORDE            | R175 |

| 5.20 | Out-of-order GATS epoch progression with MPI_WIN_ACCESS_AFTER_EXPOSURE_                |      |

|      | REORDER                                                                                | 175  |

| 5.21 | Out-of-order GATS epoch progression with MPI_WIN_EXPOSURE_AFTER_EXPOSURE_       |     |

|------|---------------------------------------------------------------------------------|-----|

|      | REORDER                                                                         | 176 |

| 5.22 | Out-of-order GATS epoch progression with MPI_WIN_EXPOSURE_AFTER_ACCESS_         |     |

|      | REORDER                                                                         | 177 |

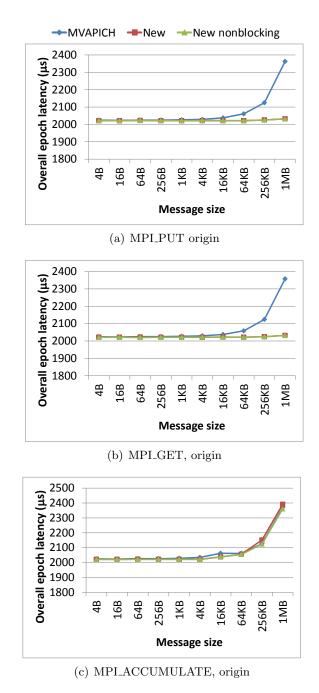

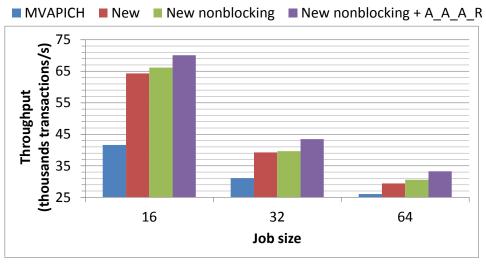

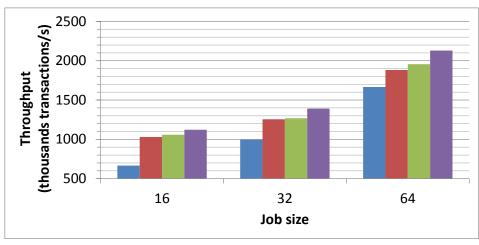

| 5.23 | Performance of a dynamic unstructured transactional communication pattern .     | 178 |

| 5.24 | Wall-clock CPU time spent in communication wait phases                          | 181 |

| 5.25 | Overall wall-clock CPU time spent in communication activities                   | 182 |

| 5.26 | Overall wall-clock CPU time spent solving LU                                    | 183 |

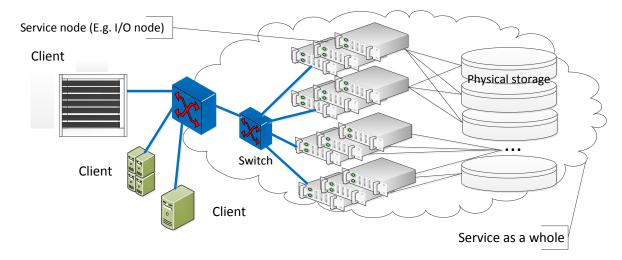

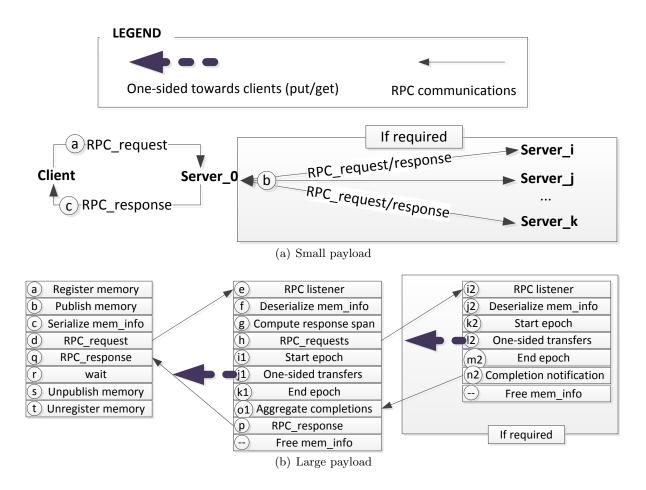

| 6.1  | Distributed storage service                                                     | 189 |

| 6.2  | I/O transfer protocol                                                           | 190 |

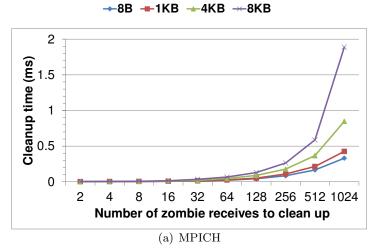

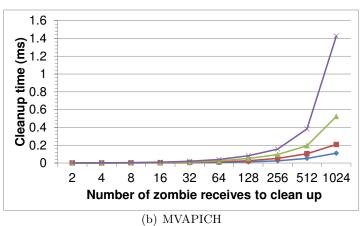

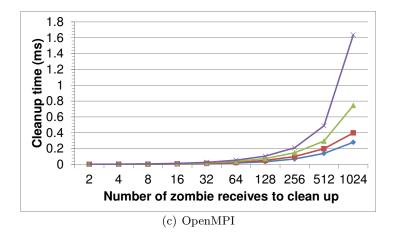

| 6.3  | Zombie receive cleanup latency                                                  | 205 |

| 7.1  | Theoretical optimal message queue dimensionality in terms of communicator sizes | 227 |

# List of Equations

| 3.1  | Overall duration of serialized communication and computation                     | 52  |

|------|----------------------------------------------------------------------------------|-----|

| 3.2  | Overall duration of overlapped communication and computation                     | 52  |

| 3.3  | Overall duration of overlapped communication and computation for $c_p > c_m$     | 52  |

| 4.1  | Rank as linear combination of powers of dimensionSpan                            | 68  |

| 4.2  | dimensionSpan in terms of communicator size                                      | 70  |

| 4.3  | Purely dimensional decomposition speedup trend                                   | 74  |

| 4.4  | Additional speedup brought by array-based dimension modeling                     | 74  |

| 4.5  | Communicator size threshold for small/large sub-queue                            | 76  |

| 4.6  | Linked list search complexity without rank wildcard                              | 82  |

| 4.7  | Linked list search complexity with rank wildcard                                 | 82  |

| 4.8  | Insertion/deletion complexity                                                    | 82  |

| 4.9  | Array search complexity without rank wildcard                                    | 82  |

| 4.10 | Array and 4D UMQ search complexity with rank wildcard                            | 83  |

| 4.11 | Array PRQ search complexity with rank wildcard                                   | 84  |

| 4.12 | 4D search complexity without rank wildcard                                       | 85  |

| 4.13 | 4D PRQ search complexity with rank wildcard                                      | 85  |

| 4.14 | Linked memory consumption                                                        | 90  |

|      | Array memory consumption                                                         | 91  |

|      | 4D memory consumption                                                            | 91  |

| 4.17 | Number of JumpPoints                                                             | 91  |

| 4.18 | Number of Cubes                                                                  | 91  |

| 4.19 | Memory overhead of the array with respect to the linked list                     | 91  |

| 4.20 | Memory overhead of the 4D data structure with respect to the linked list $\dots$ | 91  |

| 4.21 | Memory overhead of the array with respect to the red-black tree                  | 96  |

| 5.1  | Earliest data transfer time                                                      | 129 |

| 5.2  | Effect of Late Post on next activity with blocking epochs                        | 131 |

| 5.3  | Effect of Late Post on next activity with nonblocking epochs                     |     |

| 5.4  | Effect of Early Fence on next activity with blocking epochs                      | 132 |

| 6.1  | Number of simultaneous work items in terms of number of CPU cores                | 213 |

| 6.2  | Deadlock condition                                                               |     |

| 6.3  | Deadlock avoidance condition                                                     |     |

| 6.4  | Absolute safety condition                                                        | 214 |

| 6.5  | Concise absolute safety condition                                                |     |

| 6.6  | Opposite of concise absolute safety condition                                    |     |

| 6.7  | Infinite simultaneous concurrent work items                                      | 215 |

# List of Code Listings

| 6.1 | Client-side connection code snippet                | 196 |

|-----|----------------------------------------------------|-----|

| 6.2 | Server-side connection code snippet                | 196 |

| 6.3 | Client-side disconnection code snippet             | 197 |

| 6.4 | Server-side disconnection code snippet             | 197 |

| 6.5 | Server-side nonblocking disconnection code snippet | 216 |

# Acronyms

AEF Application Execution Flow. 45

API Application Programming Interface. 14

**ARMCI** Aggregate Remote Memory Copy Interface. 5

ASL Average Search Length. 111

**CPU** Central Processing Unit. 1

CQ Completion Queue. 28

CQE Completion Queue Entry. 28

CTS Clear To Send. 34

**DDR** Double Data Rate. 28

EDR Enhanced Data Rate. 28

FDR Fourteen Data Rate. 28

**FLOPS** Floating Point Operations Per Second. 2

**GATS** General Active Target Synchronization. 20

HCA Host Channel Adapter. 28

**HPC** High Performance Computing. 1

IBA InfiniBand Architecture. 28

IBTA InfiniBand Trade Association. 28

**IETF** Internet Engineering Task Force. 34

MASL Max Average Search Length. 111

MPI Message Passing Interface. 2

MQI Message Queue Item. 60

MQL Max Queue Length. 111

MTBF Mean Time Between Failures. 7

MX Myrinet Express. 30

NAS NASA Advanced Supercomputing. 53

NIC Network Interface Card. 26

**OFED** OpenFabrics Enterprise Distribution. 30

**OS** Operating System. 13

PAMI Parallel Active Messaging Interface. 29

PCIe Peripheral Component Interconnect Express. 27

**PEF** Parasite Execution Flow. 45

**PGAS** Partitioned Global Address Space. 2

**POSIX** Portable Operating System Interface. 47

PRQ Posted Receive Queue. 60

QDR Quad Data Rate. 28

**QP** Queue Pair. 28

**RDMA** Remote Direct Memory Access. 26

RMA Remote Memory Access. 3

RPC Remote Procedure Call. 189

RTR Ready To Receive. 36

RTS Ready To Send. 34

SDR Single Data Rate. 28

SRQ Shared Receive Queue. 29

TCP Transmission Control Protocol. 26

uGNI user Generic Network Interface. 30

UMQ Unexpected Message Queue. 60

**WQE** Work Queue Entry. 28

## Chapter 1

### Introduction

High Performance Computing (HPC) or *supercomputing* is the use of computing systems of large computational power to solve complex problems. HPC aims for speed of computation. Among other things, supercomputers are used for completing in a few hours computing activities that would take decades or centuries on mere workstations. It was a time where supercomputers were reserved only for governments, powerful corporations and select academic institutions. Back then, the immediate benefits of advances in HPC were reserved for a tiny fraction of the scientific community. Recently, however, HPC has evolved from fulfilling the sole needs of genomics, physics, ocean or astronomy research to become a powerful tool for just about any scientific research field and for industry as well. Psychologists are relying on supercomputers for knowledge retrieval and translation. Supercomputers are also routinely used for high frequency stock trading. More generally, any individual who is concerned about the next cancer cure, daily weather forecasting or fraud detection by credit card companies, etc., is already depending on HPC at unprecedented levels. Supercomputing has become a fast-paced research field that propells science, engineering, economy or even entertainment.

Like 84.6% of the 500 most powerful systems as of November 2013, the typical supercomputer is a cluster [106]; that is, a distributed system made of multiple compute *nodes* linked in a high speed *network*. Each node is usually a standalone multicore compute element. An HPC program, usually called *job* at runtime, is made of multiple processes distributed over the Central Processing Unit (CPU) cores of the cluster. The distributed nature of clusters

establishes communication as one of their key aspects. Communication is a collaboration mechanism which allows the tasks in an HPC job to frequently exchange data or intermediate results with their peers. Communication is actually the single element that determines performance when computation must cross node boundaries. As a consequence, the efficiency of the communication subsystem of clusters tends to get a lot of attention in supercomputing research. Armed with decades of experience, and with performance at the core of its concerns, the HPC community has maintained programming paradigms, referred to as message passing, which allow explicit communication between the numerous CPU cores of clusters. The most widespread embodiment of these paradigms is the Message Passing Interface (MPI) [68]. MPI, which is a standardized paradigm whose specification is maintained by the MPI Forum [68], is the default programming tool delivered with nowadays' top supercomputers. MPI is also believed to remain a key player in supercomputing [9, 33]. In fact, for being so widely supported on existing supercomputers and for being the implementation vehicle of the massive amount of existing HPC code base, MPI remains a support even for newly emerging programming paradigms [9, 64, 98] such as the Partitioned Global Address Space (PGAS) languages [114]. Justifiably, MPI is a place to bring major and immediately impactful software-level improvements in supercomputing.

The performance of a supercomputer is measured in Floating Point Operations Per Second (FLOPS); and a major goal of HPC research is to squeeze out larger and larger amounts of FLOPS from supercomputers. With the large number of CPU cores found in supercomputers, parallelism becomes the means of creating performance. However, parallelism tends to suffer a diminushing return effect. For a given job, the 10000<sup>th</sup> CPU core does not necessarily add the same number of FLOPS as the first and the second processors. This concern is just one of the many issues that are considered scalability-related. Scalability is concerned with how to create sustained performance growth via hardware and software evolution. Scalability is also concerned with how to get existing and new HPC jobs to leverage the performance growth.

Nowadays top supercomputers [106], such as Tianhe-2, Titan-Cray XK7 or Sequoia, are petaflops-capable machines; that is, their performance can reach the order of 10<sup>15</sup> FLOPS. Nevertheless, just like nowadays' supercomputers allow feats that were impossible a decade

ago, there is more to accomplish that the impressive 33.86 petaflops of Tianhe-2 are still inadequate for. Justifiably, the HPC community is seeking to push the scales even further; with the goal of reaching an exaflop (10<sup>18</sup> FLOPS) by the end of the current decade. MPI and its various implementations have a key mandate in reaching the exascale goal; and for that purpose, their scalability effort must become less lenient on some seemingly benign serialization issues. A comprehensive scalability approach must also emcompass non communication-related aspects of HPC jobs at large scales. Examples of non communication-related concerns are resiliency and memory consumption not linked to data transfer. This dissertation focuses on specific changes required for MPI to successfully fulfill its partition of the challenges inherent to creating sustainable performance growth on nowadays' and future system scales.

#### 1.1 Motivation

Any MPI activity that can generate and propagate latency is a potential scalability issue. Any MPI activity whose resource consumption pattern is linear or superlinear is a potential scalability issue as well. Latency propagation can create a snowball effect whose overall impact depends on how many processes are involved. In general, every MPI communication can have impacts beyond the sole processes that it involves. A single delay in any communication can transitively impact all the other processes of a job by propagating to subsequent communications or computations. As scales grow, latency propagation tends to become more and more harmful.

MPI offers three programming models. They are two-sided communications, also called point-to-point communications; one-sided communications, also called Remote Memory Access (RMA); and collective communications. These three communication models are defined in depth in Chapter 2; but as a quick introduction, a two-sided communication involves a sender and receiver both issuing a communication call. The parameters of both calls must match for the send operation to be consumed at the receiver side. One-sided operations occur between two processes. However, unlike two-sided operations, they do not have any concept of reception. Conceptually, only one process does the communication. The one-sided initiator can remotely

load or store data into another peer; sometimes unbeknownst to the process which owns the memory region manipulated by the initiator. Collective communications involve multiple peers. A collective communication either allows a process to send or receive from all the peers in a certain group of processes, or allows all the processes in a given group to simultaneously send and receive from one another.

The MPI one-sided communication is an example of major MPI feature that inherently bears serialization and latency propagation in its very specification. MPI RMA occurs inside *epochs* which are critical section-like regions enclosed by synchronizations calls. The synchronization calls that close the epochs are blocking; and because their execution can involve internal communication between multiple peers, they can generate and propagate latency; on top of explicitly creating communication/communication or communication/computation serialization.

For more than 15 years, the one-sided communication model of MPI has failed to generate enthusiasm and adoption. Nevertheless, the adoption level of MPI as a whole has never ceased to increase; meaning that MPI has done pretty well even without an accepted onesided communication model. So, why would it matter now to worry about the MPI one-sided communication model? First, one-sided communications in general are supposed to be less subject to latency propagation than two-sided communications. Since only the initiator is involved in the data transfer, one-sided communications are decoupled from the availability of the receiving end. As a result, they offer more potential for avoiding initiator-generated latency from delaying the remote peer; and vice-versa. This reduced level of interaction is scalability-friendly. As proof of one-sided communication adequacy for nowadays and future HPC concerns, one can notice its strong prevalence in modern supercomputing network technologies. In fact, modern network technologies [6, 44, 54, 57] put forth prominent one-sided communication features. Some of those modern interconnection technologies even offer only one-sided models of communication at the core of their operating modes. InfiniBand [44], which is the most prevalent networking family in the 500 most powerful supercomputers [106] is one such example. Similarly, the Portals networking API [6], which is used by the Cray supercomputers, is built around one-sided semantics. The emerging PGAS family of HPC programming languages [114] are also built over one-sided communication frameworks such as the Aggregate Remote Memory Copy Interface (ARMCI) [105] and GASNet [99]. Furthermore, new classes of programs which perform unstructured communications [115] are extremely challenging to realize efficiently in situations where each sent message must be matched by a receive. In these situations, one-sided data transfers become the viable communication model; opening up the path for a whole set of dynamic, loosely synchronous patterns of computations.

The one-sided communication model is not an alternative to two-sided communication; it brings its own features. As virtue of MPI being the most portable and the default programming framework uniformly delivered with new supercomputers, MPI RMA is the most accessible one-sided programming model available. There is an important advantage to portability in supercomputing because of the disparity in system architectures [106, 120]. In particular, there is an advantage to being able to run the same cancer research HPC code on Tianhe-1, Tianhe-2, the Japanese K computer, any Blue Gene system or any Cray architecture; and even on future unknown supercomputer architectures [120]. Currently, such a source-level portability guarantee is the exclusivity of MPI. As a result, MPI is the place to truly leverage the many positive characteristics of one-sided communications for scalable HPC and the support of emerging communication patterns. The very specification of MPI one-sided communications needs a scalability-driven improvement.

Sometimes, latency propagation and serialization issues are not the consequence of how the communication is specified in the MPI standard; they are peculiar to the concrete realization of the specification. It is customary in MPI to enforce parallelism between communication and computation via nonblocking communication routines. A nonblocking communication is broken into the initiation phase which is nonblocking and the completion phase which must block until the data transfer completes. The initiation phase, which corresponds to the actual communication routine call, could potentially exit before the data transfer completes. Then the data transfer is expected to occur in parallel with any computation that is inserted between the two phases. The resulting parallelization between the data transfer and the inserted computation is called *communication/computation overlapping*. Communication/computation overlapping is meant for mitigating the communication latency. Thus, for a communication

that lasts  $C_m$  and a computation that lasts  $C_p$ , the overall duration of both activities is the maximum of  $C_m$  and  $C_p$  instead of the sum of both as it is the case when serialization occurs. However, in many cases, even when communication/computation is expressed with the means provided by MPI at application level, the data transfer is simply internally deferred to the completion phase and occurs after the communication; leading to the very serialization that the specified behaviour was intended to avoid. In particular, when the payload of a two-sided communication is beyond a certain size, a handshake-based protocol called *Rendezvous* is used to negotiate buffer availability before the data transfer occurs. In nonblocking communications, the Rendezvous protocol can fail to achieve communication/computation overlapping. Several solutions put forth various designs of the protocol but they miss at least one scenario where the workarounds that they propose fail to be applicable [16, 65, 80, 85, 95, 96]. Another category of solutions fixes the problem in a comprehensive way but the very designs used by these solutions bear scalability issues because of their resource consumption patterns [56, 102]. The problem in this case resides in coming up with an adequate design of the Rendezvous protocol that is scalable and that fulfills two-sided communications without serialization.

Another major scalability source in MPI resides in its message queues. Message queues are not particularly linked to any specified feature of MPI. However they are internally very involved in MPI communications fulfilment. The impossibility for a process to consume in a timely fashion all the messages sent by the numerous peers running on other CPU cores inside the same or on remote nodes is just one of the many reasons why messages must be queued at receiving ends. Message queues are actually not specific to MPI; they are a fundamental mechanism used to work around the limited nature of resources such as memory buffers and other objects required for message reception and processing [6]. Message queues are used so frequently in MPI that they have been qualified as its most crucial data structures [49]. In fact, the performance of certain communication-intensive HPC jobs is simply determined by the underlying MPI message queue processing. Long message queue processing accounted for up to 60% of the communication latency in tests presented in [109]. It has been observed that MPI message queues grow with job sizes and scales [12, 13, 14, 49]. With the current and upcoming system scales, it has become imperative to approach MPI message queues in

ways that account for the massive amount of peers each process can potentially communicate with. In particular, a modern and scalability-conscious message queue must not only remain reasonably fast at extreme scales, but it must account for the amount of memory resource that each CPU core can afford to reserve for an exponentially growing number of remote CPU cores to interact with.

Beyond all these specific and communication related issues that could be a hindrance to scalability, one must also be concerned about all the non-communicating aspects of MPI. Systems running with MPI are delivering quadrillions of FLOPS nowadays. As the HPC community is planning for the exascale by the end of the current decade, there is consensus among authors that profound architectural and programming behaviour shifts will be required [22]. MPI has gone through many major scalability-induced shifts in the past; but there are challenges that have never been encountered in any of the previous shifts. An example of one such challenges is the reduced Mean Time Between Failures (MTBF) issue that is anticipated at exascale [22, 50]. What happens if on average large MPI-based HPC jobs cannot run to completion before the next failure occurs? Would those jobs then become impossible to run to completion on average? Another issue is resource exhaustion management. How does MPI impact the HPC application when it runs out of internal memory? In fact, the scalability challenges of MPI are not limited to how to reach larger scales; they also include what happens to HPC programs once they can run at those large scales. Certain corner cases of past and nowadays scales will undoubtedly become normal operating conditions and will have to be dealt with, not as exceptional situations, but as regular HPC program execution events. Those situations are tagged "corner cases" because they are rare, difficult to reproduce and occur only in extreme conditions. For MPI to remain viable at extreme scales, those corner cases must nevertheless be revealed ahead of reaching exascale and provisioned for.

#### 1.2 Problem Statement

The hardware manufacturers are realizing the amazing feat of periodically releasing supercomputers with faster network fabrics and larger CPU core counts. To the question of how to run

an HPC program on those powerful and massive systems, the answer largely lies in MPI. MPI is undoubtedly changing along with the systems it runs on; but how timely or complete are those changes for the growing concern that is scalability? At a finer granularity, this dissertation answers the following questions:

- 1. How to approach the Rendezvous protocol of data transfer in a comprehensive way and without introducing new scalability issues?

- 2. For being a central aspect of MPI middleware, how to make sure that MPI message queues remain fast when job sizes grow? What data structure design approach can fulfill that speed goal without exhibiting an impractical pattern of memory consumption?

- 3. How does MPI evolves its one-sided communication model to make it viable and attractive for HPC program use? In particular how to solve the issue of blocking synchronization and remove the resulting serialization and latency propagation without introducing consistency hazards in the memory regions touched by one-sided communications?

- 4. Beyond its obvious duty of transferring data between the processes of an HPC job, what other forward-looking scalability-related trait does MPI still lack; and how to reveal those traits and justify their importance? For instance, what happens when MPI runs out of memory to create its internal objects? What happens when an isolated peer becomes unresponsive in a very large group of processes? What facility does MPI provide for the custom resiliency needs of programs whose lifetimes are expected to include various kinds of partial failures? How do the non communication-related MPI features impact scalability?

#### 1.3 Contributions

This dissertation addresses specific MPI issues which impact scalability. In Chapter 3, we show how efficient two-sided message progression in MPI falls short of the expectations in spite of the existence of autonomously progressing HPC network devices. The discussion is based on two-sided data transfers, which is the main communication model covered by the MPI

literature on the message progression issue. The message progression issue shows up only in certain scenarios. On the one hand, there are the existing solutions which always miss at least one of the problematic cases. On the other hand, the solutions which cover all the problematic scenarios tend to adopt a brute force approach where their proposed fixes are applied even in the issue-free cases. As a consequence, the overhead associated with the fixes is incurred by the HPC application even when it is not justified. In Chapter 3, we approach the two-sided message progression with a proposal that brings the following contributions:

- A solution which can deterministically detect the specific scenarios where message progression fails to occur in a timely fashion. By applying a solution only in these scenarios, the overhead associated with our proposed fix is incurred only if it is justified.

- Memory-scalability thanks to the absence of a dedicated message progression thread for every single MPI process.

In Chapter 4 we show that message queue processing is very prevalent in MPI. Then we describe the impact of next generation HPC performance-oriented features on how often MPI message queues are solicited. We expose the scalability shortcomings of mainstream message queue designs and show how they render the resources available per CPU core inadequate for MPI processes at large scales. In particular, the chapter documents previous message queue designs which become quickly unusable for large jobs because they are scalable with respect to only one of speed of operation or memory consumption; but not both. Then, we present a novel multidimensional MPI message queue design which solves the aforementioned scalability problem by considerably mitigating the effects of job size on both speed of operation and memory consumption. To the best of our knowledge, the work of Chapter 4 represents the first two-fold scalable message queue architecture of MPI. The proposed message queue puts forth the following contributions:

- Considerable reduction of the length of linear searches in MPI message queues. We actually ensure that linear searches grow considerably slower compared to job sizes.

- Deterministic detection and skipping of very large portions of queue items which are guaranteed to be irrelevant during searches. This dimensionality-based narrowing down

of the search leads to very slow search performance degradation as system and job sizes tend towards extreme scales. A special case of this contribution leads to the early detection of unfruitful searches. Therefore, major latency reductions can be achieved by preventing a receiving process from incurring potentially large search penalties to no avail.

• Amortized memory consumption and decreasing rate of memory consumption growth with respect to the queue size.

Chapter 5 presents an analysis of why MPI RMA falls short of meeting the one-sided communication expectations of the HPC community. We show the specific burdens that the MPI RMA synchronization model, which supports the epochs, puts on HPC applications. Chapter 5 brings the following contributions:

- Proposal of the first known MPI RMA improvement that completely removes the epoch serialization constraint; allowing one-sided communication lifetimes to effectively be nonblocking from start to finish.

- True decoupling between processes participating in MPI one-sided communications.

- First proposed correction to classes of latency issues inherent to MPI RMA. The serialized nature of MPI RMA epochs were the cause of six kinds of latency propagation issues first documented in [55] as the "MPI one-sided inefficiency patterns". Four out of the six inefficiency patterns had no remedy or workaround prior to the work covered in Chapter 5.

- Discovery of a new class of latency issue inherent to MPI RMA as specified in MPI-3.0, the latest version of the MPI standard. The new issue, which is also an inefficiency pattern is documented for the first time by the work covered by Chapter 5. A solution is brought to this new inefficiency pattern as well.

- Possibility to more efficiently realize in MPI a new class of HPC programs. In concrete terms, the proposed nonblocking RMA synchronizations allow HPC programs with dynamic and unstructured communication patterns to be expressed in MPI without large

performance hit created by high contention levels.

Finally, we create in Chapter 6 unusual conditions of use and reveal many of the MPI limits at large scales. The experience leads to proposals to overcome these limits. The contributions of Chapter 6 are as follows:

- Presentation of the first known use of MPI as the network transport for extreme-scale distributed storage services.

- Demonstration of the scalability and safety tradeoff imposed by the blocking nature of non-communicating MPI routines. The proof leads to establishing the importance of nonblocking flavours of non-communicating MPI routines as the solution to certain cases of scalability issues that cannot be solved even if CPU cores were available in abundance in each node.

- Discussion of how the ability of cancelling communications can be a powerful primitive for custom resiliency mechanisms in software running on top of MPI. By making a practical experimentation-backed case for a cancellation-friendly MPI, we provide a conceptual approach to mitigating the MTBF issue anticipated for exascale systems.

- Creation by the storage service of conditions that naturally demonstrate at moderate scale the behaviour of major MPI implementations in situations of resource exhaustion. From the observed behaviours, we construct recommendations for MPI to sustain resource-demanding HPC jobs at large scales.

#### 1.4 Dissertation Outline

The rest of this dissertation is organized as follows. Chapter 2 presents background material on the typical software and hardware layers that support HPC jobs. An emphasis is put on MPI in its general structure as well as its specific features that are exploited later in the document. HPC network technologies are covered briefly as well. Chapter 3 gives an in-depth survey of Rendezvous-based message progression approaches in MPI and discusses methods that we investigated for improving message progress engines in certain scenarios. Chapter 4

provides a deep analysis of MPI message queues and shows why they are not adapted to the current and future job scales. Then, a new message queue design, with scalability as a primary concern, is described. Chapter 5 discusses MPI one-sided communications as it is currently specified. Then, the chapter presents the proposals brought by this dissertation to close the gap between MPI and the HPC community expectations. Chapter 6 presents our experience in using MPI in unconventional settings. The experience culminates in revealing a use case-backed list of scalability-oriented features that MPI currently lacks. Finally Chapter 7 concludes and introduces future work.

### Chapter 2

# Background

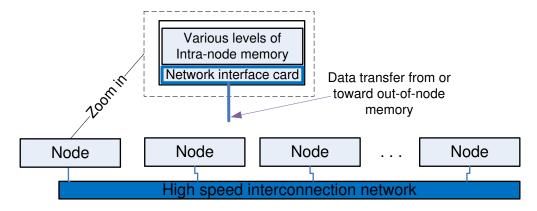

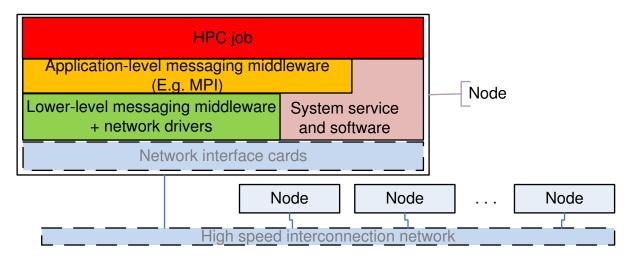

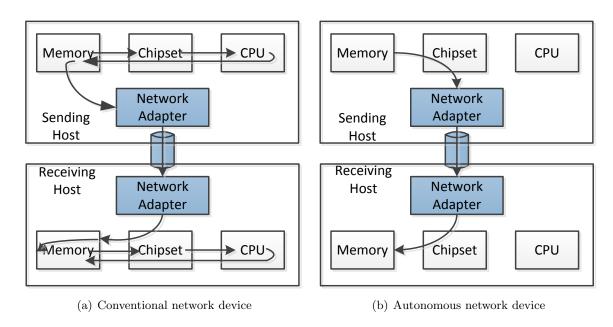

An HPC cluster is composed of a large number of compute nodes interconnected via a high speed network. From a hardware perspective (Figure 2.1), the memory hierarchy of a cluster has one additional level compared to a standalone workstation. For each node, the additional memory level is the remote memory of each of the other nodes; and since it is external, it is reached via the high speed network. Data transfer between memories of distinct nodes is expressed in the form of communication to the application-level messaging middleware (Figure 2.2), such as MPI, which is generic and network-device agnostic. The communication is fulfilled by the network device which is reached via a lower-level network-specific messaging middleware. In the stack, every level can resort to generic system software mechanisms such as memory allocation.

Each node can host one or several tasks; depending mostly on the number of CPU cores that it possesses. The unit of task execution in an MPI context is a process. From an Operating System (OS) point of view though, the unit of execution is a thread; an entity that requires exactly a single CPU core to execute without contention. By default, a process is single-threaded; that is, it possesses a single thread and requires a single CPU core. Processes can also be multithreaded in which case they host several threads and can exhibit parallelism internally. The following subsections describe the components of the stack as well as HPC network technologies.

Figure 2.1: HPC cluster: Intra-node and out-of-node memory view

Figure 2.2: HPC cluster: software stack view

#### 2.1 Message Passing Interface (MPI)

Application-accessible messaging middleware are used to shield the HPC programmer from many system and network-level intricacies. In supercomputing, messaging middleware typically use the message passing model. MPI, which is the convergence of a few early messaging models, drives the advances in supercomputing thanks to its large prevalence as the HPC programming paradigm.

MPI is a standardized paradigm. The specification, maintained by the MPI forum [68], defines a language-independent Application Programming Interface (API) focused on portability. A binding is explicitly specified for C and Fortran; but implementations are possible in other languages. The current version 3.0 of the MPI specification has been released in September

2012 to supersede the previous MPI 2.2 standard. MPI-3.0 is the maturation of 18 years of effort following the release of the first MPI standard in 1994. MPI enforces a data-locality conscious programming by allowing only explicit communications between processes.

MPI manages processes in sets called *groups*. Groups are not usually manipulated in communications; instead, the programmer is presented with *communicators*, which define a communication scope or universe where each belonging process is uniquely identified by a *rank*. A rank is meaningful only in the scope of a communicator. In fact, the same process can have as many distinct ranks as the number of communicators it belongs to. Communicators can be of two types: *intracommunicators* and *intercommunicators*. An intracommunicator is conceptually no different from the group mapped to it. An intercommunicator is made of two groups that act exclusively as source or destination universes in a communication. The MPI application programmer can create communicators on-demand; and each user-created communicator can contain any non-empty subset of the existing processes. However, MPI provides the following predefined communicators which always exist by default in any job:

- MPI\_COMM\_WORLD: A communicator whose group encompasses all the processes.

- MPI\_COMM\_SELF: A communicator whose group is made only of the invoking process.

Each process has its own MPI\_COMM\_SELF.

- MPI\_COMM\_NULL: The empty communicator.

An important mechanism of any MPI implementation is the progress engine, which ensures that any issued communication is handled to completion. The MPI progress engine takes care of transferring data as well as detecting and expressing transfer completion. Three MPI implementations have found widespread acceptance in the HPC community for being freely available at source-level for research and production. They are MPICH [69], MVAPICH [71] and Open MPI [79]. MPICH, maintained by the Argonne National Laboratory, is the reference implementation and the base source code for many other MPI implementations optimized for some specific high performance interconnects. Custom versions of MPICH are used on the large Blue Gene [28] and Cray supercomputers [36]. Many commercial MPI implementations such as Microsoft-MPI and Intel-MPI are also MPICH-derivatives. MVAPICH, maintained

by the Ohio State University, is an MPICH-derivative which targets openly-specified modern network technologies such as iWARP [86] and InfiniBand [44]. Open MPI is an attempt to concentrate in a single distribution the advantages of three previous MPI implementations namely, LAM/MPI, LA-MPI and FT-MPI [26]. Although it has been around only since 2006, Open MPI has found an important level of adoption due to the widespread use of some of its building block implementations such as LAM/MPI [25].

In the rest of the dissertation, we stick with the case convention of the MPI specification. This convention uses all uppercase letters for language-agnostic MPI functions and constants. For instance the communicator creation routine is written MPI\_COMM\_CREATE. When a C binding is explicitly used, only the first five letters of routines are capitalized. For instance, the C version of the communicator creation routine is written MPI\_Comm\_create. Constants are still all uppercase in the C binding.

#### 2.1.1 Datatypes and Derived Datatypes in MPI

Communications in MPI transfer arrays of data. The payload is thus always described by a datatype and a count. MPI provides many predefined datatypes which map to regular datatypes in programming languages such as C or Fortran. Examples of predefined MPI datatypes are MPI\_CHAR, MPI\_WCHAR, MPI\_SHORT, MPI\_INT, MPI\_FLOAT, MPI\_DOUBLE, MPI\_LONG, MPI\_UNSIGNED\_LONG, etc. MPI even defines an address-sized type, MPI\_AINT, that can be used in memory offset computations.

Sometimes however, certain messages cannot nicely be described as arrays of simple datatypes. Thus, MPI allows the programmer to define arbitrary datatypes by composing existing ones. Those custom types are referred to as derived datatypes. MPI allows the creation of contiguous and noncontiguous datatypes to describe messages with arbitrary gaps in their spanning memory addresses. A derived datatype can be made of other derived datatypes at an arbitrary level of nesting. Derived datatypes can be expressed as structures, vectors, indexed or hindexed types. An indexed datatype allows replication of an existing datatype, derived datatype included, into a sequence of blocks. The offset of each block in the new derived datatype is expressed as a multiple of the composing datatype size. An hindexed datatype is similar to an

indexed datatype; except that the displacements are expressed in bytes.

#### 2.1.2 Two-sided Communications

A two-sided communication, simply termed point-to-point or two-sided, involves only two processes and a send/receive semantics. A point-to-point message is uniquely identified at the sender side by the triple (communicator, receiver\_rank, tag); and by (communicator, sender\_rank, tag) at the receiver side. The triple provided by the receiver call must match the one provided by the sender for a two-sided communication to complete. However, instead of providing a specific source rank or tag, the receiver can provide MPI\_ANY\_SOURCE or MPI\_ANY\_TAG which are wildcards meant to respectively match any sender process in the same communicator or any tag. Wildcards allow the expression in MPI of communication patterns required by certain applications.

MPI\_SEND) will not return until the data buffer being sent is safe to modify without compromising the content meant to be delivered. Safe to modify might mean that the data is buffered into some user-inaccessible system or middleware buffer and still pending transmission. Non-blocking sends/receives allow an MPI application to express communication/computation over-lapping. A nonblocking send (e.g., MPI\_ISEND) returns immediately but the programmer is responsible for guaranteeing that the application's sent data buffer is not modified until it is safe to do so. A blocking receive (MPI\_RECV) blocks until the data is received. A nonblocking receive (MPI\_IRECV) exits immediately but transfers to the programmer the responsibility of guaranteeing the integrity of the receive buffer until the reception completes. For both send and receive, the process can check, if required, when a pending nonblocking transfer has completed. Nonblocking two-sided must always be paired with one of the *test* or *wait* family of routines described in Section 2.1.5. Both blocking and nonblocking send operations are available in different flavours in order to either control system buffer use or to minimize the out-of-sync problems inherent to matching send/receive requests.

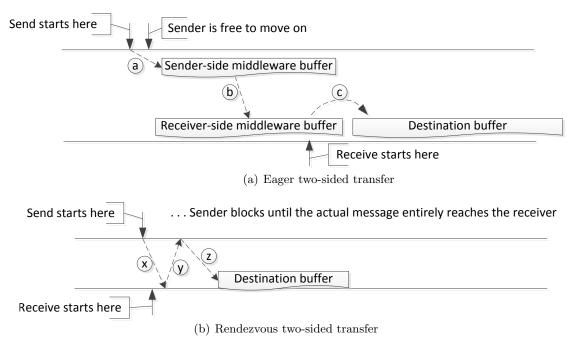

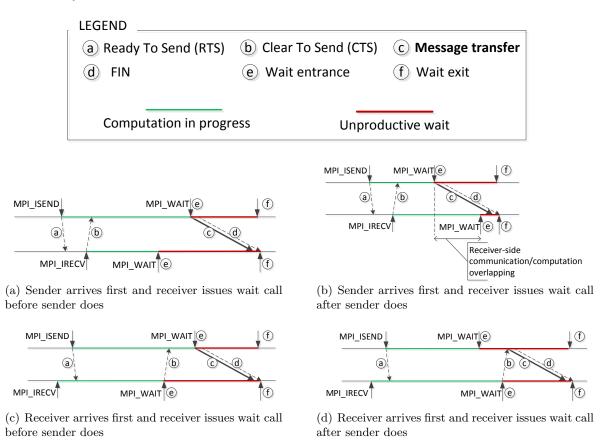

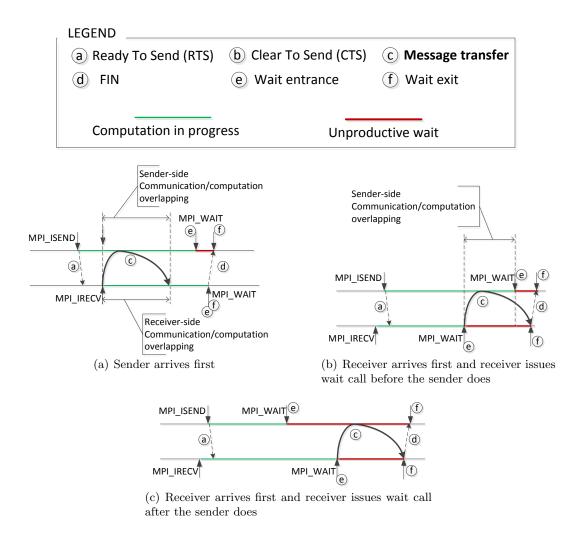

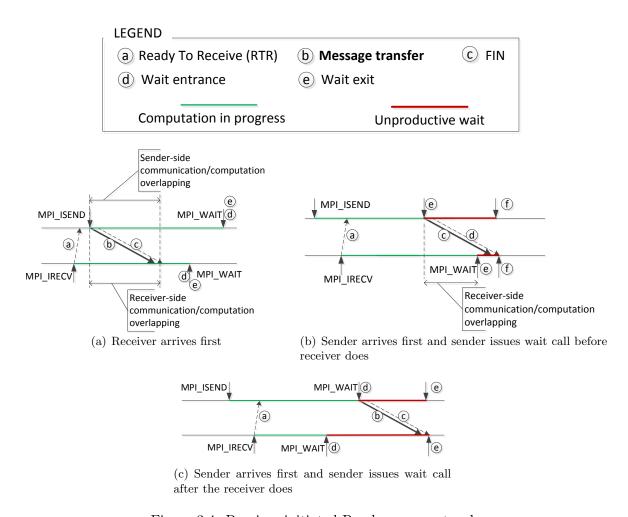

MPI implementations usually put forth two protocols for point-to-point message transfers. The first one, the *Eager* protocol, allows the sender to buffer the message and proceeds without waiting for a late receiver (Figure 2.3(a)). More generally, a message is said to be sent eargerly when the receiver is not notified of its arrival ahead of time. The Eager protocol is suitable only for small messages because it does an intermediate copy (step b in Figure 2.3(a)). Buffer copy is expensive for large messages. Additionally, middleware buffers are limited and cannot accommodate large messages. As a consequence, a handshaking (steps x and y in Figure 2.3(b)) is required for large messages so that the peer taking care of the transfer could know both the source and final destination addresses in order to perform a single and final message copy (step z in Figure 2.3(b)). The arrows x and y in Figure 2.3(b), called control messages, can bear various information such as the aforementioned buffer addresses. A control message is an internal message generated to ease MPI operation; it does not transfer application-level data. This handshaking-based approach of Figure 2.3(b) defines the second point-to-point protocol named Rendezvous.

LEGEND: a:=sender-side buffering | b:=Eager message transfer and receive-side buffering | c:=copy to final destination | x,y:=handshaking | z:=direct Rendezvous data transfer

Figure 2.3: Two-sided message transfer protocols

Figure 2.3(a) purposely shows a late receiver so as to emphasize the usefulness of the Eager protocol. The receiver being early does not change the steps of the Eager protocol.

As for Figure 2.3(b), it depicts a very simplified version of the Rendezvous mechanism; the goal here is to simply distinguish between the two protocols. The actual engineering of the Rendezvous protocol can be complex; a deeper coverage of the Rendezvous-based point-to-point communication is deferred to Chapter 3. We emphasize that both Eager and Rendezvous data transfer approaches are middleware-level protocols; they are not visible at the application level.

#### 2.1.3 Collective Communications

Collective operations, simply called *collectives*, involve all the processes in the communicator over which they occur. Collectives define three different semantics, namely, collective communication-computation (e.g., MPI\_REDUCE), data distribution (e.g., MPI\_BCAST) and synchronization (e.g., MPI\_BARRIER). A collective communication/computation performs some distributed computation along with the data distribution. A collective synchronization does not transfer any application-level data; it simply guarantees that all the processes of a communicator have reached a certain point in the execution. Collective operations are also offered in different flavours characterized by whether the same amount of data is sent to all the participating processes. Some collective operations can be rooted, in which case a single process, called *root*, sends to or receives from all the other ones in the communicator. If a collective operation is not rooted, all the participating processes are senders and receivers at the same time. Collectives can also be blocking or nonblocking. Finally, a class of MPI communications, called *neighborhood collectives* allows collectives to occur over a group of processes whose layout or *topology* is known. The goal of neighbourhood collectives is to allow the MPI middleware to optimize the scheduling of the rounds of messages that make up the collective.

#### 2.1.4 One-sided Communications

The MPI standard introduced its one-sided communication model in 1997. MPI RMA communications happen over objects called *windows* which define 1) the memory region that each process intends to expose for remote access and 2) the communication scope encompassing a set of processes.

In MPI RMA, the process reading or writing the remote memory is called the origin

while the one whose memory is being acted on is called the *target*. MPI RMA occurs in critical section-like regions called *epochs*. An epoch is defined by a pair of opening and closing synchronization constructs. When an epoch is over, all its contained RMA communications are guaranteed to have completed for the concerned process. In one-sided communications, the origin process specifies all the communication parameters where the target process remains passive.

#### **MPI RMA Synchronizations**

MPI defines two classes of RMA synchronizations, namely active target where the target explicitly opens an epoch to match origin-side epochs; and passive target where the target does not even need to make epoch calls. There are two kinds of active target epochs; and they are Fence and General Active Target Synchronization (GATS). All three kinds of epochs are shown in Figure 2.4. The MPI\_PUT and MPI\_GET calls shown in Figure 2.4(a) are examples of RMA communication calls; they are covered later in this section. In a fence epoch (Figure 2.4(a)), each participating process is simultaneously origin and target and can issue RMA communications to any peer in the communication universe covered by the window object. A single fence can also serve as both closing an epoch and opening the next one. For instance the sequence  $Fence_0 - Epoch_0 - Fence_1 - Epoch_1 - Fence_2$  is correct; and means that  $Fence_1$ closes  $Epoch_0$  and opens  $Epoch_1$  at the same time. For the sake of reference later in the document, we designate such a unique call which separates two adjacent fence epochs as a middle fence. MPI allows assertions meant to guarantee that a fence call is not a middle fence. MPI\_MODE\_NOPRECEDE, when provided with a fence call, informs the middleware that the routine only opens a new epoch. MPI\_MODE\_NOSUCCEED tells the middleware that the current fence call only closes a previously opened epoch.

In a GATS synchronization, in a given epoch, a process is either origin or target but not both. In Figure 2.4(b), *Process0* and *Process2* are origins. Each of them opens an *access epoch* towards a group of targets. In Figure 2.4(b), the target group is only made of *Process1* which opens an *exposure epoch* for a group of origins. In a GATS synchronization, an origin can only communicate with the group of processes specified at epoch opening time (MPI\_WIN\_START).