# NODE-WIDE ASYNCHRONOUS MESSAGE PROGRESSION FOR EFFICIENT & SCALABLE COMMUNICATION IN HIGH PERFORMANCE COMPUTING

By

#### KAUSHAL KUMAR

A thesis submitted to the

Department of Electrical & Computer Engineering

in conformity with the requirements for

the degree of Master of Applied Science

Queen's University

Kingston, Ontario, Canada

(December, 2016)

Copyright © KAUSHAL KUMAR, 2016

## **Abstract**

High Performance Computing (HPC) has served as the enabler for several scientific and engineering accomplishments. Consequently, there has been an ever-increasing demand to create larger and faster high performance systems. To efficiently utilize the HPC resources, parallel applications rely on software that abstract the cluster hardware. Currently, the most prominent software abstraction standard in HPC is the Message Passing Interface (MPI). Parallel applications entail communications to synchronize and to share intermediate results. To minimize the duration of application executions, it is crucial to overlap such communications with the computations.

The MPI standard specifies three messaging semantics, namely, point-to-point communication, one-sided communication and collectives. In point-to-point communication, the overlap of large payloads has been a problem and there have been several proposals to address this. Among these approaches, asynchronous message progression is more adoptable because of its ability to deal with a wider range of inefficiencies and its non-reliance on specialized hardware. Traditional asynchronous message progression approaches have relied on either polling or interrupt based threads. The polling based approach is more responsive but is resource-intensive. On the other hand, the interrupt based approach is resource-efficient but is associated with overheads. This thesis proposes a node-wide asynchronous message progression technique that offers the advantages of both polling and interrupt based approaches, while minimizing or eliminating their adverse effects. This approach was found to be scalable, incur negligible overheads, induce the ideal amount of overlap in most scenarios of point-

to-point communications and cast a small memory footprint. This technique was found to improve the overlap of certain collectives as well.

One-sided MPI communication offers the ability to transfer messages with few or no synchronizations, regardless of the payload size. This scheme promotes overlaps but there are several overlap inhibiting scenarios. This thesis proposes a similar asynchronous message progression technique to address such scenarios. The one-sided implementation was able to achieve overlap in the different inefficient scenarios, with negligible overheads and a small addition to the memory footprint.

## Acknowledgements

First and foremost, I would like to extend my sincerest gratitude to my supervisor, Dr. Ahmad Afsahi, without whom this dissertation would not have been possible. I am deeply indebted to him for his constant guidance, encouragement and unwavering support over the last two years. I am also indebted to Dr. Judicael Zounmevo for his insights and for the knowledge that he has imparted to me. My heartfelt gratitude to the members of the thesis defense committee, Dr. Thomas Dean, Dr. Ying Zou and Dr. Steven Blostein for their insightful comments and questions. I would like to thank the Natural Science and Engineering Research Council of Canada (NSERC) for supporting this research through grants to my supervisor. I am also thankful to Queen's University for supporting me financially through awards and teaching assistantships.

I would like to thank the HPC Advisory Council and Mr. Pak Lui for providing the resources and technical support for this research. I am also very grateful to our Graduate Program Assistant, Ms. Debra Fraser for helping me with academic and administrative matters.

I would like to express my heartfelt gratitude to my colleagues at the Parallel Processing Research Laboratory for the wonderful times that we have shared. Iman, Hessam, Mahdieh, Mac and Priya, I will cherish your friendships forever. I also thank my fellow graduate students for their company and the thought-provoking discussions.

Last but not the least, I would like to thank my parents for their patience and unquestioning support over the years.

## Table of Contents

| Abstract                                         | ii  |

|--------------------------------------------------|-----|

| Acknowledgements                                 | iv  |

| Table of Contents                                | v   |

| List of Figures                                  | ix  |

| Glossary                                         | xii |

| Chapter 1: Introduction                          | 1   |

| 1.1 Motivation                                   | 3   |

| 1.2 Problem Statement                            | 5   |

| 1.3 Contributions                                | 7   |

| 1.4 Outline                                      | 9   |

| Chapter 2: Background                            | 11  |

| 2.1 HPC Clusters                                 | 12  |

| 2.1.1 Remote Direct Memory Access and InfiniBand | 13  |

| 2.1.2 NUMA Based Compute Node                    | 16  |

| 2.1.3 Parallel Programming Paradigms             | 17  |

| 2.2 Shared Memory Model                          | 18  |

| 2.3 Partitioned Global Address Space Model       | 19  |

| 2.4 Message Passing Model                        | 19  |

| 2.4.1 Point-to-point Communication               | 20  |

|    |      | 2.4.2 Collective Communications                                                                                                                                                                                                          | 27                                           |

|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|    |      | 2.4.3 One-Sided Communication                                                                                                                                                                                                            | 29                                           |

|    | 2.5  | Summary                                                                                                                                                                                                                                  | 37                                           |

| Ch | apte | r 3: Literature Review                                                                                                                                                                                                                   | 39                                           |

|    | 3.1  | Point-to-Point Communication                                                                                                                                                                                                             | 40                                           |

|    |      | 3.1.1 Inefficiencies Associated with the Rendezvous Protocols                                                                                                                                                                            | 40                                           |

|    |      | 3.1.2 Literature Review                                                                                                                                                                                                                  | 44                                           |

|    | 3.2  | One-Sided Communication or Remote Memory Access (RMA)                                                                                                                                                                                    | 53                                           |

|    |      | 3.2.1 Inefficiencies Associated with RMA Synchronizations                                                                                                                                                                                | 53                                           |

|    |      | 3.2.2 Literature Review                                                                                                                                                                                                                  | 56                                           |

|    | 3.3  | Summary                                                                                                                                                                                                                                  | 57                                           |

| Ch | apte | r 4: Node-Wide Asynchronous Message Progression for Point-to-Point                                                                                                                                                                       |                                              |

|    |      |                                                                                                                                                                                                                                          |                                              |

|    |      | Communication                                                                                                                                                                                                                            | 60                                           |

|    | 4.1  | <b>Communication</b> Motivation                                                                                                                                                                                                          | 60<br>61                                     |

|    |      |                                                                                                                                                                                                                                          |                                              |

|    |      | Motivation                                                                                                                                                                                                                               | 61                                           |

|    |      | Motivation  Design of SmartInterrupts                                                                                                                                                                                                    | 61<br>62<br>66                               |

|    |      | Motivation  Design of SmartInterrupts                                                                                                                                                                                                    | 61<br>62<br>66                               |

|    | 4.2  | Motivation                                                                                                                                                                                                                               | 61<br>62<br>66<br>66                         |

|    | 4.2  | Motivation                                                                                                                                                                                                                               | 61<br>62<br>66<br>66<br>68                   |

|    | 4.2  | Motivation                                                                                                                                                                                                                               | 61<br>62<br>66<br>66<br>68<br>69             |

|    | 4.2  | Motivation  Design of SmartInterrupts  4.2.1 Choosing the Default Rendezvous Protocol  4.2.2 Asynchronous Message Progression Mechanism  4.2.3 Core Components  Implementation of SmartInterrupts  4.3.1 Interrupt Handler Kernel Module | 61<br>62<br>66<br>66<br>68<br>69             |

|    | 4.2  | Motivation                                                                                                                                                                                                                               | 61<br>62<br>66<br>68<br>69<br>69<br>70       |

|    | 4.3  | Motivation                                                                                                                                                                                                                               | 61<br>62<br>66<br>68<br>69<br>69<br>70<br>73 |

|       | 4.5.2 Two-Sided Micro-Benchmarks                                   | 78  |

|-------|--------------------------------------------------------------------|-----|

|       | 4.5.3 Collective Micro-Benchmarks                                  | 87  |

|       | 4.5.4 Application Results                                          | 92  |

| 4.6   | 5 Summary                                                          | 94  |

| Chapt | er 5: Node-Wide Asynchronous Message Progression for One-Sided     |     |

|       | Communication                                                      | 96  |

| 5.    | Motivation                                                         | 97  |

| 5.2   | 2 Design of SmartInterrupts for One-Sided Communications           | 101 |

|       | 5.2.1 Asynchronous Message Progression Mechanism                   | 103 |

|       | 5.2.2 Core Components                                              | 106 |

| 5.3   | 3 Implementation of One-Sided SmartInterrupts                      | 107 |

|       | 5.3.1 Shared Buffers                                               | 107 |

|       | 5.3.2 Helper Process and Interrupt Thread                          | 108 |

| 5.4   | Performance Evaluation and Analysis                                | 109 |

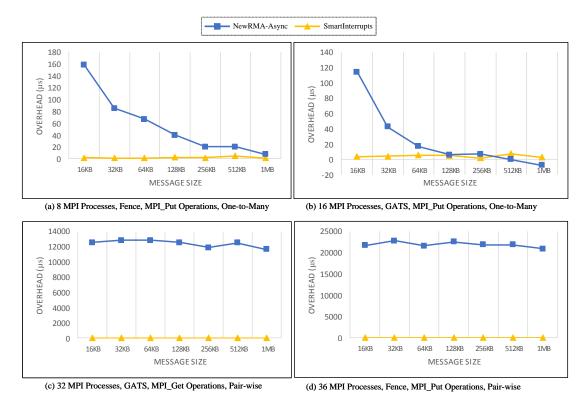

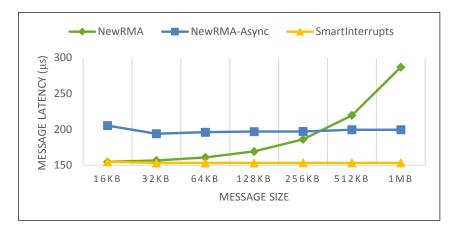

|       | 5.4.1 Fence and GATS One-Sided Micro-Benchmarks                    | 110 |

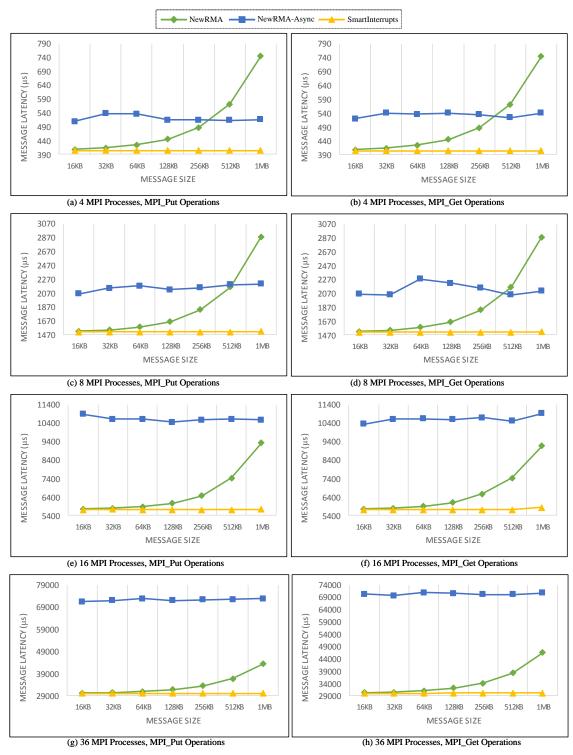

|       | 5.4.2 Exclusive Lock One-Sided Micro-Benchmark                     | 116 |

|       | 5.4.3 Memory Footprint Analysis                                    | 121 |

|       | 5.4.4 Application Results                                          | 122 |

| 5.5   | 5 Summary                                                          | 123 |

| Chapt | er 6: Conclusion and Future Work                                   | 126 |

| 6.1   | Summary of Findings                                                | 127 |

| 6.2   | 2 Future Work                                                      | 129 |

|       | 6.2.1 Unifying One-Sided and Two-Sided Designs                     | 129 |

|       | 6.2.2 Improving the Performance of SmartInterrupts for Collectives | 130 |

|       | 6.2.3 Eliminating Futile Interrupts in One-Sided SmartInterrupts   | 131 |

| Bibliography |                                                              | 133 |

|--------------|--------------------------------------------------------------|-----|

| 6.2.5        | Investigating Multi-threaded MPI Applications                | 132 |

| 6.2.4        | Dynamically Enabling/Disabling the SmartInterrupts Mechanism | 131 |

# List of Figures

| 2.1 | Illustration of a Commodity Cluster                                           | 13 |

|-----|-------------------------------------------------------------------------------|----|

| 2.2 | Comparison of Copy Mechanisms between TCP/IP and RDMA                         | 14 |

| 2.3 | Anatomy of a NUMA Compute Node                                                | 17 |

| 2.4 | Sender Initiated Rendezvous Protocols (Sender Arriving First Scenario)        | 22 |

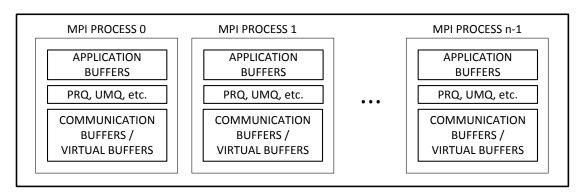

| 2.5 | Hierarchy of Buffers in Common MPI Implementations                            | 24 |

| 2.6 | Comparison of Communication/Computation Overlap between Blocking and          |    |

|     | Non-Blocking Two-Sided Calls in RDMA Read Rendezvous Protocol                 | 28 |

| 2.7 | MPI 3.1 RMA Synchronizations                                                  | 31 |

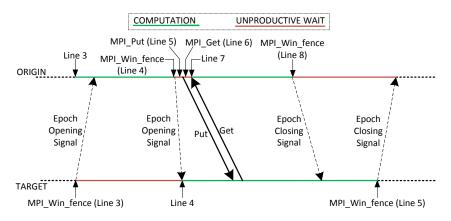

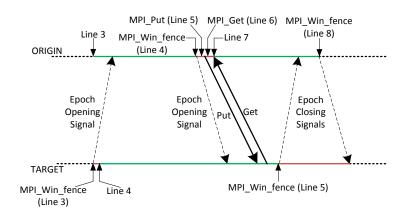

| 2.8 | Comparison of Unproductive Waits with Blocking and Non-Blocking RMA           |    |

|     | Synchronization Calls                                                         | 36 |

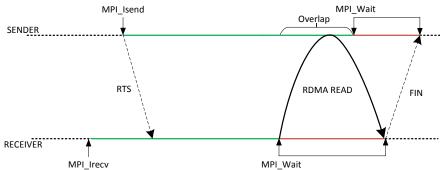

| 3.1 | Sender Initiated RDMA Read Based Rendezvous Protocols                         | 41 |

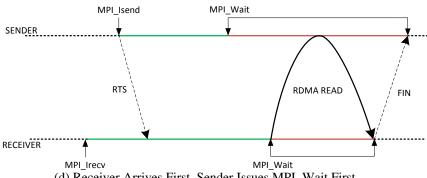

| 3.2 | Sender Initiated RDMA Write Based Rendezvous Protocols                        | 42 |

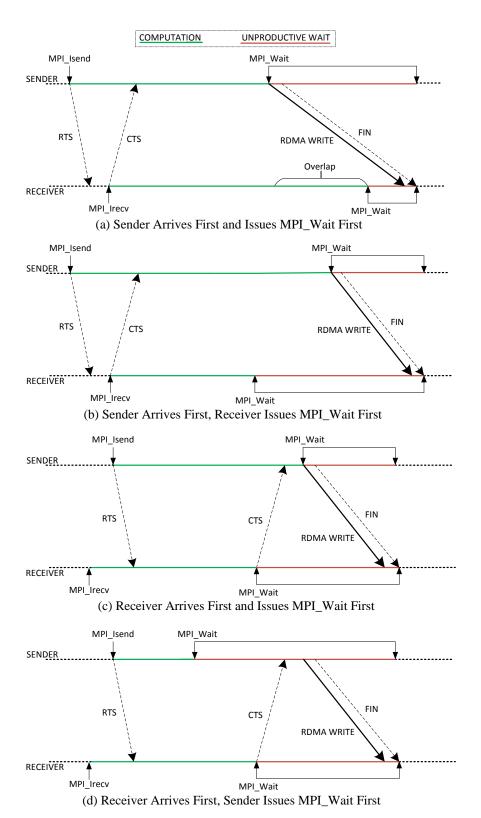

| 3.3 | Receiver Initiated RDMA Write Based Rendezvous Protocols                      | 45 |

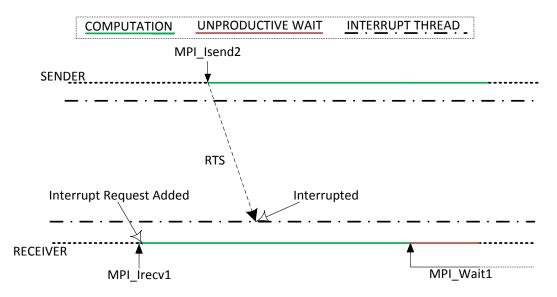

| 3.4 | Interrupt Thread based Asynchronous Progression                               | 52 |

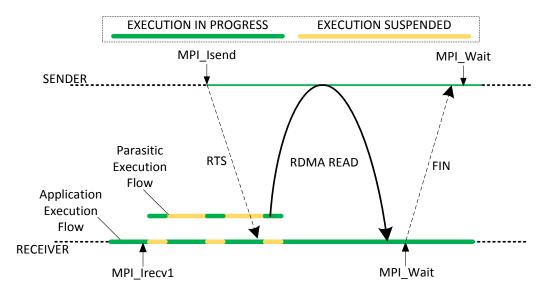

| 3.5 | Illustration of Parasitic Execution Flow Based Asynchronous Message Progressi | on |

|     | (Adapted from [87])                                                           | 53 |

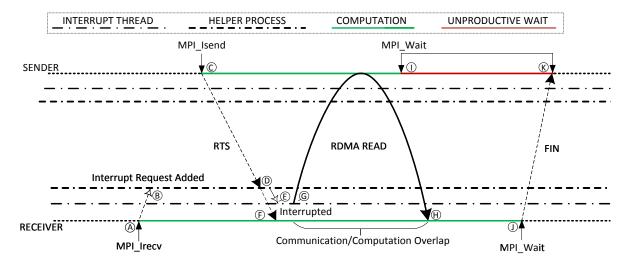

| 4.1 | Data Movement and Signals in Smart Interrupts                                 | 67 |

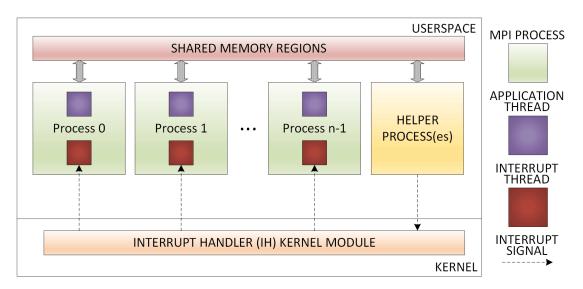

| 4.2 | Core Components of SmartInterrupts                                            | 69 |

| 4.3 | Illustration of Buffers and Data Movement in SmartInterrupts                  | 71 |

| 4.4  | Pair-wise Communication in Two-Sided Micro-Benchmarks                        | 79   |

|------|------------------------------------------------------------------------------|------|

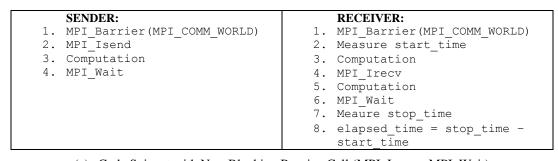

| 4.5  | Template for Two-Sided Micro-Benchmark Design                                | 80   |

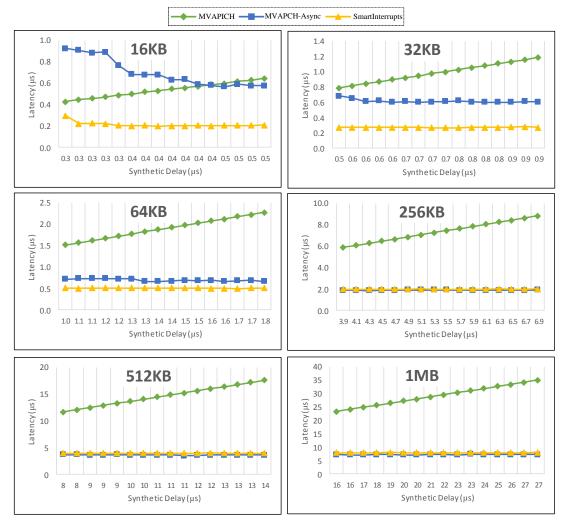

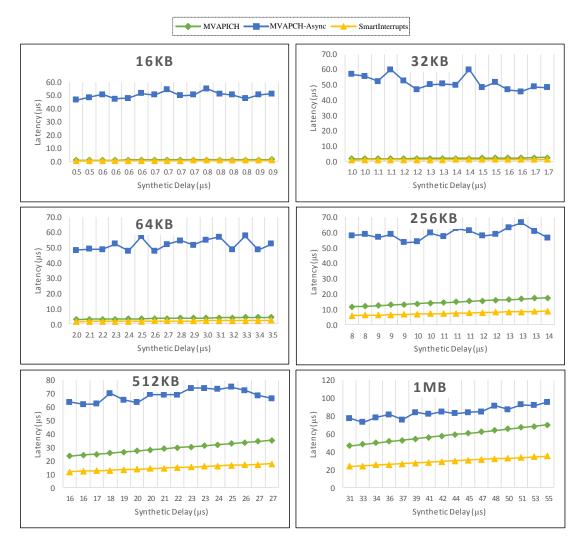

| 4.6  | Two-Sided Latency Overhead Results over MVAPICH                              | 82   |

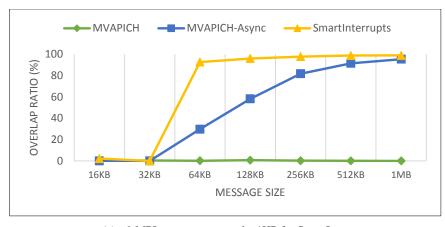

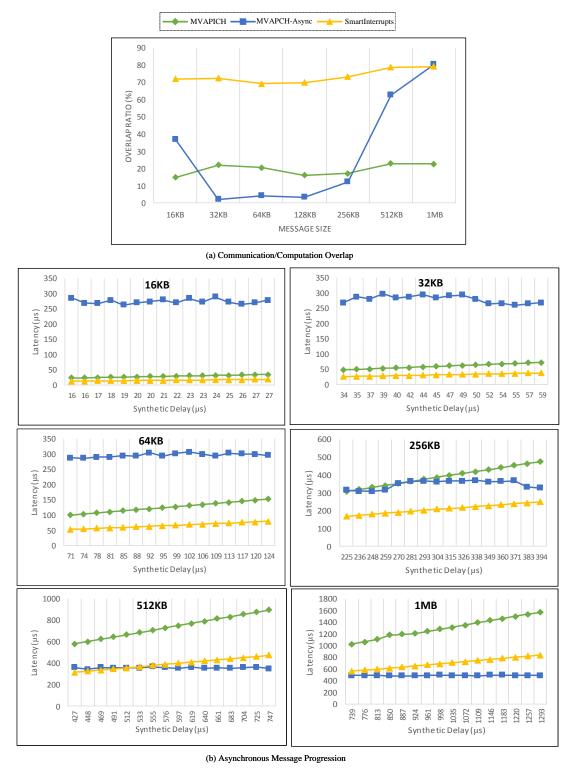

| 4.7  | Communication/Computation Overlap of Point-to-Point Communications           | 84   |

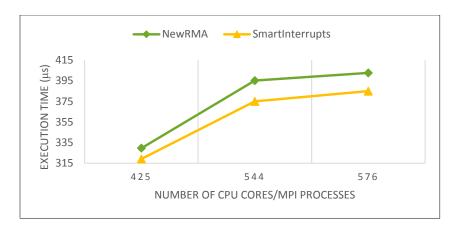

| 4.8  | Scalability Analysis of Two-Sided SmartInterrupts                            | 85   |

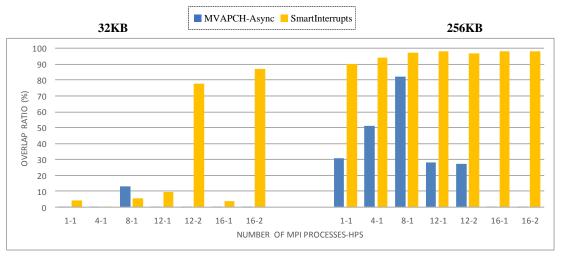

| 4.9  | Asynchronous Message Progression for 9 MPI processes per node, 1 Helper Pro- | cess |

|      | for Smart Interrupts                                                         | 87   |

| 4.10 | Asynchronous message progression for 18 MPI processes per node, 2HPs for     |      |

|      | SmartInterrupts                                                              | 88   |

| 4.11 | Template for Collective Micro-Benchmark Design                               | 89   |

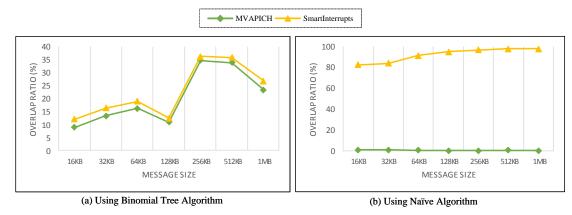

| 4.12 | MPI_Ialltoall Overlap and Asynchronous Message Progression Results           | 90   |

| 4.13 | MPI_Igather Micro-benchmark Results                                          | 92   |

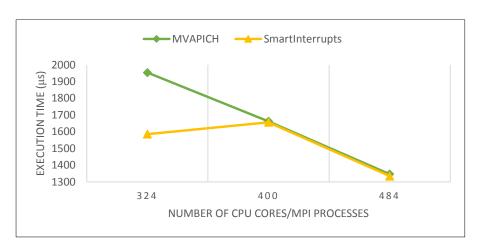

| 4.14 | NAS-SP Results                                                               | 93   |

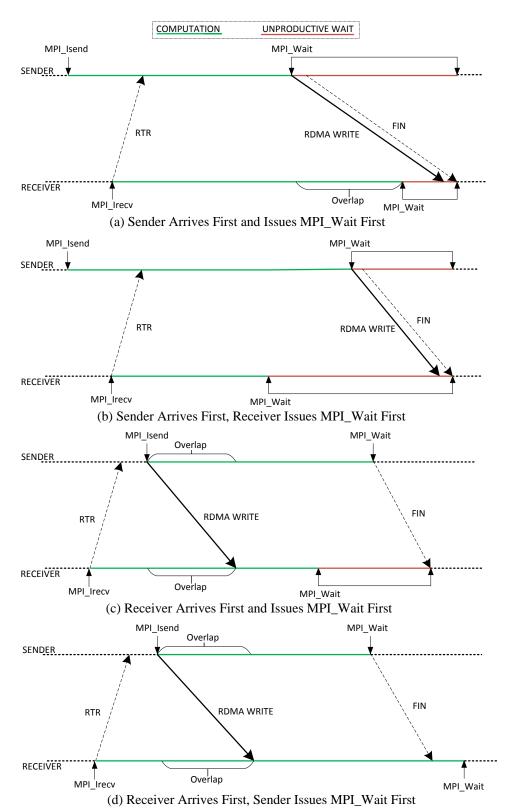

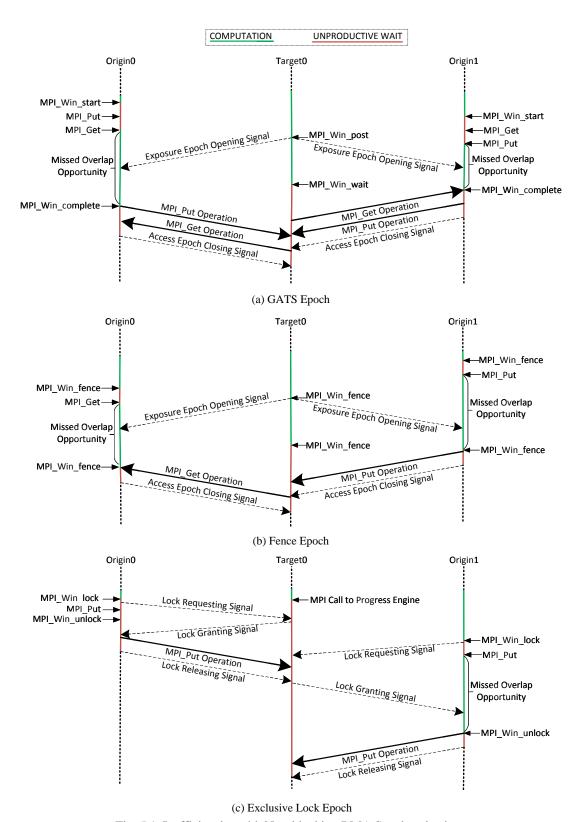

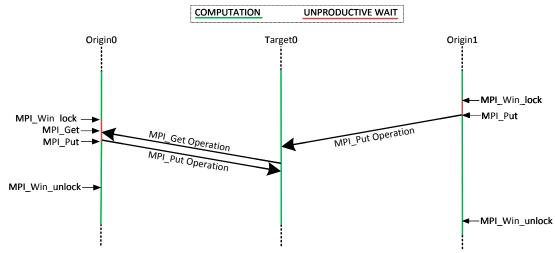

| 5.1  | Inefficiencies with Non-blocking RMA Synchronizations                        | 98   |

| 5.2  | Illustration of Communication/Computaiton Overlap with Shared Lock Epochs .  | 100  |

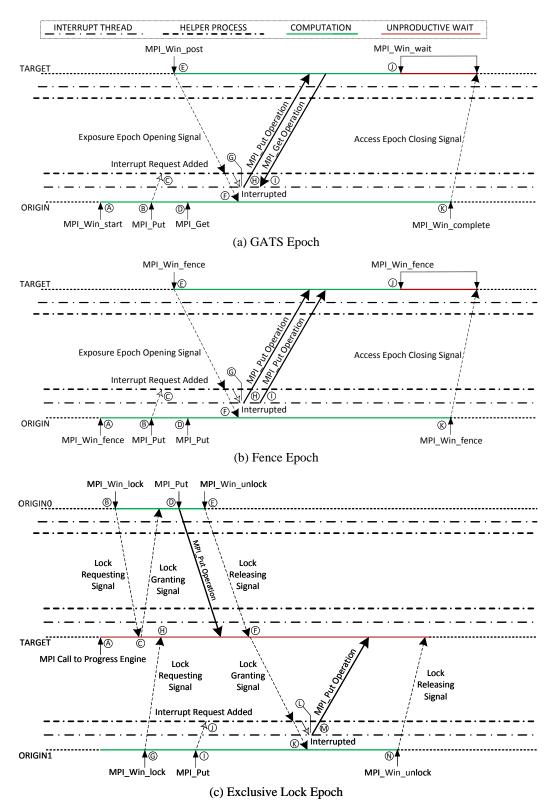

| 5.3  | Data Movement and Signals in One-Sided SmartInterrupts                       | 104  |

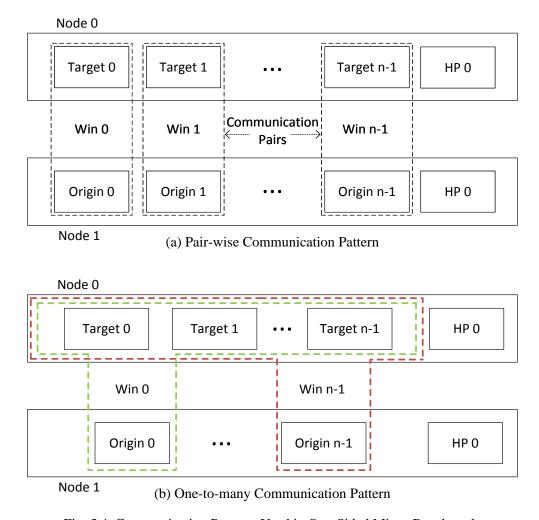

| 5.4  | Communication Patterns Used in One-Sided Micro-Benchmarks                    | 111  |

| 5.5  | Template for One-Sided Latency Overhead Micro-Benchmark                      | 113  |

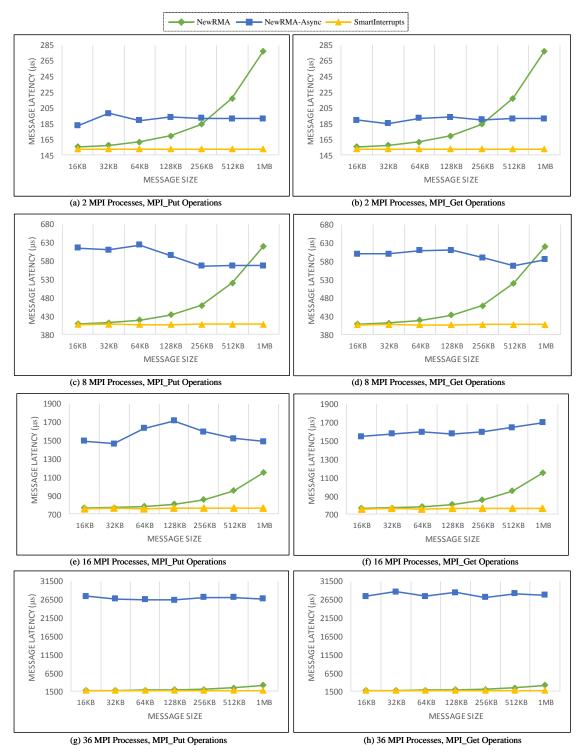

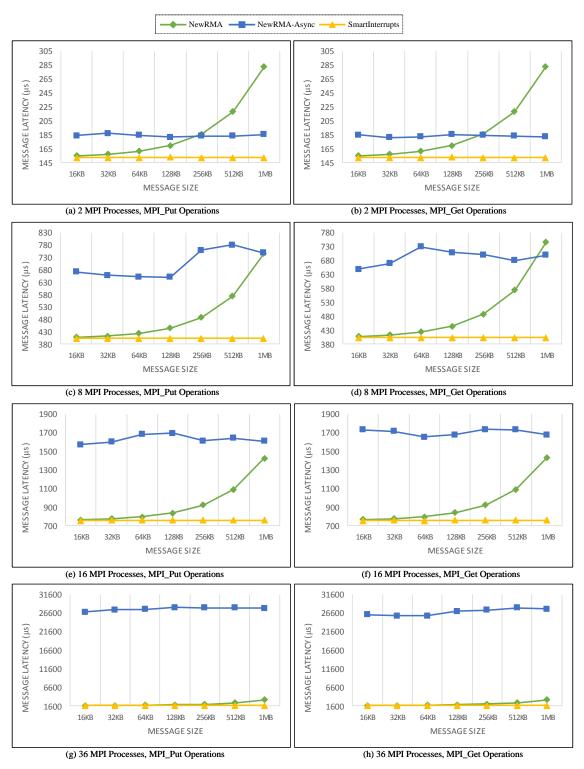

| 5.6  | One-Sided Latency Overhead Results with Fence and GATS                       | 114  |

| 5.7  | Template for Fence & GATS Communication\Computation Overlap                  |      |

|      | Micro-Benchmark                                                              | 115  |

| 5.8  | One-Sided Overlap Results for Fence Epochs with Pair-Wise Communication      |      |

|      | Pattern and 1 HP                                                             | 117  |

| 5.9  | One-Sided Overlap Results for GATS Epochs with Pair-Wise Communication       |      |

|      | Pattern and 1 HP                                                             | 118  |

| 5.10 | One-Sided Overlap Results for Fence Epochs with One-to-Many Communication |    |

|------|---------------------------------------------------------------------------|----|

|      | Pattern and 1 HP                                                          | 19 |

| 5.11 | One-Sided Overlap Results for GATS Epochs with One-to-Many Communication  | 1  |

|      | Pattern and 1 HP                                                          | 20 |

| 5.12 | Template for Exclusive Lock Communication\Computation Overlap             |    |

|      | Micro-Benchmark 1                                                         | 21 |

| 5.13 | Overlap Micro-benchmark Results for Exclusive Lock Epochs with 1 HP       | 21 |

| 5.14 | LU Decomposition Results with 1 Helper Process per Node                   | 23 |

# Glossary

| API Application Programming Interface      |

|--------------------------------------------|

| CQ Completion Queue                        |

| CTS Clear To Send                          |

| FLOPS Floating-Point Operations Per Second |

| GATS General Active Target Synchronization |

| GPU Graphics Processing Unit               |

| HCA Host Channel Adapter                   |

| HP Helper Process65                        |

| HPC High Performance Computing             |

| HWLOC Portable Hardware Locality           |

| ICB Interrupt Control Buffer               |

| ICD Interrupt Control Data                 |

| IPC Inter-Process Communication            |

| IRB Interrupt Request Buffer71             |

| IRD Interrupt Request Data73               |

| MP MPI Process                             |

| MPP Massively Parallel Processing          |

| MPI Message Passing Interface              |

| NAS NASA Advanced Supercomputing           |

| NIC Network Interface Card                             |

|--------------------------------------------------------|

| <b>OFED</b> OpenFabrics Enterprise Distribution        |

| OS Operating System                                    |

| PCIe Peripheral Component Interconnect Express         |

| PGAS Partitioned Global Address Space                  |

| PMPI MPI Profiling Interface                           |

| POSIX Portable Operating System Interface              |

| PRQ Posted Receive Queue                               |

| QP Queue Pair                                          |

| RDMA Remote Direct Memory Access                       |

| RMA Remote Memory Access                               |

| RTR Request To Receive44                               |

| RTS Ready To Send                                      |

| SGE Scatter Gather Element                             |

| SP Scalar Pentadiagonal92                              |

| SPE Synergistic Processing Elements                    |

| SRQ Shared Receive Queue48                             |

| TCP/IP Transmission Control Protocol/Internet Protocol |

| UMQ Unexpected Message Queue                           |

| UPC Unified Parallel C                                 |

| VBUF Virtual Buffer70                                  |

| VmRSS Virtual Memory Resident Set Size                 |

| WR Work Request                                        |

## Chapter 1

## Introduction

The speed of the computations can be enhanced by increasing the clock frequency of the processor, however, only up to a certain limit. However, power and heat dissipation requirements make it impractical to fabricate very high frequency processors [53]. Also, certain applications in science, engineering and business domains execute complex algorithms and work on large datasets that may take years, decades or even centuries to run on a single processor. The solution to this is parallel computing, in which the main problem is divided into smaller subsets and the sub-problems are solved on different processors. High Performance Computing (HPC) uses this idea to solve computationally-intensive problems on systems consisting of hundreds, thousands or even millions of CPU cores [7]. It may not be apparent, but HPC is ubiquitous. Today, HPC is a vital component of several scientific, industrial and commercial fields such as physics (nuclear, astrophysics, applied, particle, aerodynamics), biochemistry (cancer and drug research), geology, mathematics, defense, medical imaging and diagnosis, financial trading and climate modelling, to name a few.

The performance of a computer is often measured in terms of **floating-point operations per second (FLOPS)**. **Top500** [80] is an organization that uses this yardstick to rank the fastest supercomputers of the world. At the time of writing, this list featured 95 supercomputers that are capable of delivering petascale performance. Meaning, that they can perform over quadrillion (10<sup>15</sup>)

floating-point operations per second. The fastest supercomputer in the November, 2016 rankings was Sunway TaihuLight with over 10 million cores and about 93 Petaflops of compute power. Because of the ever increasing demand for HPC, this list is not expected to stagnate anytime soon, in fact, the next milestone is to reach **exascale** [3] by 2023. In the past, the high procurement and maintenance costs limited HPC access to large government agencies and wealthy corporations. The scenario today, however, is quite different due to the widespread adoption of commodity computing. This is a cost effective solution in which an HPC system can be assembled from off-the-shelf computer components instead of choosing proprietary options. Such a system is called a cluster, which is comprised of several compute nodes connected to each other by means of a high-performance network. Among other components, each compute node contains one or more processors and can be supplemented with Graphics Processing Units (GPUs) and many-core coprocessors such as Intel Xeon Phi [69]. Clusters are becoming increasingly prevalent in HPC, in fact, at the time of writing, 86 percent of the Top500 supercomputers were found to be clusters. The rest were Massively Parallel Processing (MPP) systems which are proprietary solutions.

In a cluster, the computations may be performed locally on each compute node but they communicate with each other to synchronize and exchange intermediate results. This exchange of information is accomplished by complex networking code, on top of high-speed networks, that use low-level Application Programming Interfaces (APIs). To alleviate the application programmers from this daunting task, parallel programming paradigms (or models) [6] have been introduced. Standardized programming models are also useful to facilitate the portability of application code as different clusters may have different underlying hardware. Not surprisingly, researchers think that the race to exascale computing requires as much attention on the parallel programming paradigms as the underlying hardware. One of the most prominent paradigms in HPC, that has been around for decades is the *message passing* paradigm, in which the data is exchanged between individual processes by explicit communication and synchronization. The **Message Passing**

Interface (MPI) standard is the flag-bearer of the message passing paradigm and is governed by the MPI Forum [54]. It specifies different messaging semantics and a set of API calls to facilitate communications between processes. Since its inception in 1992, the MPI standard has seen widespread acclamation by the HPC community, and it is expected to continue with its success in the years to come [29]. The flexibility that it offers and its suitability for HPC systems make it unlikely to be replaced by other paradigms in the near future. MPI can also be combined with other programming models such as shared memory [64] and PGAS [21] to form hybrid paradigms which are referred to as MPI + X, X referring to other programming models.

### 1.1 Motivation

When a serial application is parallelized, its speedup may not be equal to the amount of increase in the computational power. In other words, increasing the number of processors from one to one hundred cannot guarantee the execution time to come down to a hundredth. This is because of the necessary communications between the processors to exchange data and arrive at the final result. Therefore, the communication latency can significantly influence an application's execution time. Also, MPI applications often contain chains of processes that depend on each other. In such a situation, a delay at one process can easily propagate to the rest of the processes in the chain. Such an effect can be devastating to the performance, especially when large clusters are involved.

The frequency and volume of communications is largely dictated by the application and reducing such parameters is beyond the scope of the MPI standard. However, an effective usage of the MPI calls can improve the application performance by hiding the communication latency. That is, the MPI calls can be issued in a way such that the communication progresses in parallel with the computation. This *communication/computation overlap* is facilitated by modern interconnects, such as Intel Omni-Path [11], InfiniBand [36], iWARP Ethernet and BXI [20], in which the communication primitives can be offloaded to the **network interface card (NIC)** and the CPU

does not have to be involved throughout the length of the communication. Effective usage of MPI calls can provide the means to improve the overlap but there are scenarios where the serialization of communication and computation cannot be avoided by the application programmer. In some of these scenarios, the fundamental messaging semantics of MPI are not enough to hide the latencies of the communications. Such scenarios require optimizations to the MPI middleware or require augmenting it with support mechanisms to induce communication/computation overlap which would have not been possible with a reference MPI implementation.

The MPI standard specifies three types of communication semantics, namely, two-sided or point-to-point communications, one-sided or RMA communications and collectives. The details of these communication semantics are discussed in Chapter 2. Two-sided communication is based on a send-receive model, in which both the sender and the receiver have to explicitly issue MPI calls for a successful message transfer. On the other hand, one-sided communication is based on the direct access to the remote peer's buffer. Transfer of one-sided messages do not require MPI calls to be issued by all the involved peers. In fact, only the peer that intends to read or write data to the other peer is required to issue the MPI call. However, the transfer of an RMA message cannot be initiated until the peers have synchronized amongst themselves. This synchronization essentially grants permissions for remote memory operations. A synchronization is required again after all the RMA communications are complete. Finally, the MPI standard specifies API calls for some special communications patterns that are frequently used in parallel applications. These functions are called collectives and are usually used when more than two peers are involved. Collective calls can often be replaced by a group of two-sided or one-sided calls, however, the use of the former is generally suggested to take advantage of the middleware optimizations.

There are a large number of scientific applications based on MPI, and a huge percentage of these applications have a large codebase. Such applications are often executed over extended periods of time, therefore, the occurrence of communication/computation serializations is not

implausible. Also, because of the nature of such applications and the scale at which they are executed, even small improvements in communication/computation overlap can have a huge overall impact on the performance.

### **1.2** Problem Statement

In the context of two-sided MPI communication, a blocking call is a function that does not return until the communication is complete. Use of a blocking call ensures the serialization of computation and communication, but it cannot be avoided in certain scenarios. Also, with modern high-speed interconnects, the latency of small messages (some bytes) does not have a huge impact on the performance if it gets serialized [22]. Therefore, using blocking calls for small messages is acceptable. But, in order to observe any overlap in the application, the use of non-blocking calls is mandatory. A non-blocking two-sided call tries to initiate the communication immediately if possible, otherwise, it defers the communication for later and returns. This message is then expected to transfer when the process is involved in other activities. However, each non-blocking call has to be ultimately blocked at some point. If the message transfer happens before that time, then there is negligible waiting at that blocking call.

Point-to-point messages can be exchanged using two protocols, namely, *eager* and *rendezvous*. In the eager protocol, the sender sends the message directly to the receiver, without the need for any synchronization. On the other hand, the rendezvous protocols require synchronizations by means of control signals. With the eager protocol, there is always a 100 percent overlap but the assumption is that there will always be enough amount of registered buffer available at the receiver [34], which is an unrealistic assumption for large messages (above a few kilobytes). So, large messages are often sent using the rendezvous protocol, in which a co-ordination between the peers is required before the transfer of the message. Overlap can be achieved at either or both of the peers if certain conditions are met [67], such as the timely issuance of MPI calls and presence of enough

computation to overlap the communication with. In a reference MPI implementation, however, there might be no overlap even if these conditions are met [76]. This is possible when the control signal arrives while the process is involved in a computation. While it is busy, the control signal remains unacknowledged by it. So, even though the message transfer conditions were met, the transfer could not be initiated immediately, leading to a potentially impaired overlap.

As mentioned previously, the transfer of RMA messages cannot be initiated until there is a synchronization between the peers. A synchronization is also required after the completion of all the RMA operations. The calls for the transfer of RMA messages is always non-blocking, however, the synchronization calls can be blocking or non-blocking. Blocking synchronizations have been shown to impede communication/computation overlaps [33, 45, 88], therefore, the use of non-blocking RMA synchronizations is vital to observe overlaps [88]. Like two-sided communication, certain conditions need to be satisfied in order to overlap RMA communications with computations. If a peer does not synchronize timely or if it does so when the other peer is busy, then the RMA communications may end up being serialized. Therefore, the use of non-blocking calls does not guarantee overlaps in all scenarios. Also, unlike two-sided communications, there is no upper limit on the number of MPI processes that may be involved in RMA synchronizations, so the unproductive delays may get compounded and propagated to several other peers. This may have a significant impact on the overall performance of the application.

This thesis focuses on the above mentioned inefficiencies and tries to answer the following research questions:

1. What are the exact scenarios that inhibit communication/computation overlap in rendezvous protocols for point-to-point communications and RMA synchronizations for one-sided communication? What is the state-of-the-art in supporting communication/computation overlap in rendezvous protocols as well as RMA synchronizations?

- 2. Is it possible to develop a node-wide message progression technique that could achieve the highest possible communication/computation overlap in all scenarios for point-to-point communications? Is it possible for such a solution to be deterministic, scalable, resource efficient and with negligible overhead? Can parallel applications benefit from such a solution?

- 3. Is it possible to extend such a communication/computation overlap technique to one-sided RMA communications? Does such a solution provide a low-overhead, scalable, and resource-efficient overlap approach for one-sided communications and applications that use them?

## 1.3 Contributions

From the last section, it can be inferred that both two-sided and one-sided communications suffer from similar inefficiencies. Not surprisingly, there are similar categories of solutions for these inefficiencies, such as, protocol improvement approaches [51, 61, 66, 74] for two-sided communication or non-blocking RMA synchronizations [88], hardware-assisted approaches [20, 27, 70] and host-based approaches [34, 73, 76, 87]. One common inefficiency occurs when the send/receive or the RMA synchronization function is not called timely, that is, the other peer is so late that there is not enough computation to overlap with. The timely arrival of the peers depends a lot on the application's algorithm. Altering this at the middleware could alter the behaviour of the application itself, therefore, the application programmer must take care to avoid such situations as much as possible. Certain solutions exist for two-sided communications [51, 74] but they are associated with issues of their own. The details of these approaches are discussed in Chapter 3.

The other scenario in which an overlap might be prevented is when one of the peers tries to synchronize while the other peer is busy in a computation. In this case, the transfer of communications cannot initiate before the end of the latter's computation. One solution that has

been proven to work well for this scenario is asynchronous message progression [34, 73]. The idea behind this approach is to have a thread that is dedicated for progressing the communications. If a peer issues the send/receive or RMA synchronization call while the application threads of the other peer are busy, then the communications are initiated immediately by the asynchronous progression thread of the latter.

Chapter 3 discusses the asynchronous progression techniques that have been proposed in the literature. The problem with the current techniques is that they are either resource intensive or associated with several overheads. Also, there is no practical solution that works well for both two-sided and one-sided communications. Bearing the limitations of the current techniques in mind, this dissertation makes the following contributions:

- The idea presented in this thesis is a novel asynchronous message progression solution that can improve the overlap of two-sided communications, one-sided communications, as well as some collectives.

- 2. The existing approaches for point-to-point communication are either based on interrupts [46, 76] or polling [34]. Interrupt based approaches are resource efficient but are associated with several overheads. Polling based approaches are more responsive but since the existing techniques propose the usage of one progression thread per MPI process, this can either lead to the wastage of compute resources or cause oversubscription. The approach proposed in Chapter 4 is a node-wide message progression technique which utilizes the strengths of both polling and interrupt based approaches, while avoiding their shortcomings. It uses the available spare resources to launch processes that aid in message progression. This makes it suitable for modern compute nodes that are equipped with many-core and multi-core devices. Also, this is a deterministic approach, so it is immune to the overheads that are caused due to the erratic arrival order of the peers.

- 3. The lack of two-sided node-wide progression techniques meant that the existing micro-benchmarks could not be used to evaluate the new proposal. Chapter 4 describes a set of new micro-benchmarks for two-sided communications where multiple processes of a node may communicate at the same time.

- 4. The existing overlap techniques for one-sided communication address only a subset of the inefficiencies. Also, most these approaches work exclusively for one-sided communication only. The approach proposed in Chapter 5 is a node-wide asynchronous message progression technique that is implemented on top of NewRMA [86, 88]. NewRMA has been proven to address several RMA inefficiencies, therefore, the proposed implementation improves NewRMA and address a large subset of inefficiencies.

## 1.4 Outline

The rest of the thesis is divided into 5 chapters. Chapter 2 provides the background and lays the foundation for the following chapters. It starts by briefly discussing the different parallel programming paradigms like message passing, shared memory and PGAS. It then focuses on MPI and describes the different message passing semantics specified in the MPI standard. Chapter 3 discusses the inefficiencies that prevent communication/computation overlaps in MPI and presents a literature review of the existing approaches. Specifically, it presents an in-depth analysis of the rendezvous protocols and RMA synchronizations, and highlights the scenarios where the overlap is inhibited. Chapter 4 proposes a novel approach for improving the overlap of two-sided MPI communications. It is an asynchronous message progression technique called SmartInterrupts. This chapter describes the design and implementation of SmartInterrupts, followed by its performance evaluation. Chapter 5 extends the design of SmartInterrupts to one-sided communications. It highlights the issues that are yet to be efficiently handled in the current approaches and addresses them through SmartInterrupts. It then reports the performance results of the micro-benchmarks and

an application that were used to evaluate the proposed design. Finally, this thesis is concluded in Chapter 6 which remarks on the future scope of the research presented in this document.

## Chapter 2

## **Background**

Scientific and engineering applications execute complex algorithms that would take an impractical amount of time to run on a single processor. The executions of such applications may be sped up by using HPC, which utilizes parallel computing to run these applications on systems comprising of hundreds, thousands or millions of processors. The compute power of HPC systems are generally measured in terms of floating-point operations per second or FLOPS. This metric is used by Top500 [80] to rank the fastest supercomputers of the world. Currently, there are several petascale (10<sup>15</sup>) systems on this list and some of them employ millions of processors. However, the demand for HPC is immense and its horizons are ever-expanding. In fact, there is a strong drive among the HPC community to achieve exascale computing [3] by 2023.

This chapter is intended to provide the relevant background for the rest of the discussion in this thesis. It will introduce the HPC hardware, with a detailed discussion on RDMA and InfiniBand. This will be followed by introducing the different parallel programming paradigms such as shared memory, PGAS and message passing. The focus will then be concentrated on MPI and its different messaging semantics such as point-to-point communication, collectives and one-sided communication. With respect to these messaging semantics, this chapter also aims to discuss important concepts such as message matching, message progression and communication/computation overlap.

#### 2.1 HPC Clusters

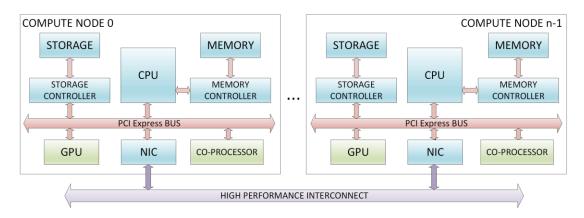

In the past, access to HPC systems was limited to government agencies and big corporations. One of the reasons for this is the relatively high monetary costs associated with proprietary solutions offered by companies such as IBM and Cray. The scenario today, however, is quite different due to the advent of commodity cluster computing. Clusters are associated with lower procurement and maintenance costs, and can be assembled using widely available components. Currently, 86 percent of the Top500 supercomputers are clusters. As illustrated in Figure 2.1, a cluster consists of several compute nodes that are connected to each other through an *interconnect*. The computations are performed on the compute nodes which use the interconnect to share the intermediate results or to synchronize. In the figure, the components inside the compute nodes that are highlighted in blue are mandatory and the ones in green are optional. The CPUs are the primary compute elements and may be supported by GPUs and co-processors. GPUs and co-processors are becoming increasingly prevalent in modern clusters. Compared to the CPUs, these have a large number of relatively low power cores and are ideal for some massively parallel applications.

As mentioned in Chapter 1, the speedup of a serial application may not scale linearly when it is parallelized. Also, increasing the parallelization usually has a diminishing return on the speedup. This is because of the necessary communications and synchronizations between the parallel tasks. In case of a cluster, this entails inter-node communications through the interconnect. In order to achieve maximum speedup, these interconnects not only have to be fast but also provide special features to optimize the communications. One such feature is to support the offloading of the communications to the network interface card (NIC). This reduces the involvement of the CPU in communications and allows it to spend more time on computations; thereby providing the possibility of overlapping the communication latencies with the computations. Today, the most prevalent high performance interconnect is **InfiniBand** [36]. In fact, at the time of writing, more

Fig. 2.1. Illustration of a HPC Cluster

than 40 percent of the top 500 fastest supercomputers use InfiniBand [80]. Other high performance interconnects include Intel Omni-Path Fabric [11], Bull eXascale Interconnect (BXI) [20], iWARP Ethernet and RoCE for clusters, and Cray Aries [24] and IBM PERCS [5] for MPP Systems. Because of its popularity, this thesis frequently refers to InfiniBand; however, the discussions and proposals presented herein are not bound to it and can be extended to other interconnects. The primary reason behind this is **Remote Direct Memory Access (RDMA)** [68], which is the common enabling technology behind most of the high performance interconnects.

## 2.1.1 Remote Direct Memory Access and InfiniBand

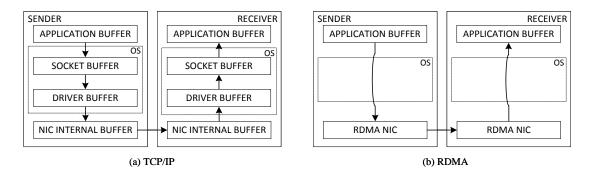

Over the years, RDMA has become synonymous with HPC networking. RDMA capable networks enable low-latency and high-throughput communications, which are desirable traits for the current petascale and future exascale systems. RDMA supports zero-copy semantics through which data can be moved between the communicating peers, without the involvement of the operating system (OS). Figure 2.2 compares the zero-copy mechanism of RDMA with the copy mechanism involved in a more traditional protocol such as TCP/IP (Transfer Control Protocol/Internet Protocol). As can be seen in the figure, TCP/IP requires copying the data at

Figure 2.2. Comparison of Copy Mechanisms between TCP/IP and RDMA

multiple intermediate locations at both the sender and the receiver, before the data reaches the target application. All these intermediate transfers require the participation of the CPU. This is not suitable for HPC applications as it would cause frequent disruptions in the computations. RDMA, however, directly deals with the address of the remote application buffer, and the data transfer is carried out by the NICs themselves. The CPU is only involved for a very short time interval to add the message transfer request to the NIC. Also, in case of a traditional interconnect such as Ethernet, the operating system is the sole owner of the NIC. Therefore, the sending application cannot access the NIC directly and must depend on the operating system to relay the information to the NIC. On the other hand, the receiving application must depend on its operating system to relay the messages that arrive on its NIC and are addressed to it. RDMA offers OS-bypass mechanisms through which the applications can directly access the NIC and send or receive data without involving the operating systems at either ends.

One of the most popular networking standards that supports RDMA natively is InfiniBand [36]. The high performance and versatility delivered by InfiniBand makes it the interconnect of choice in HPC. InfiniBand provides two transfer semantics; a channel semantic called **Send/Receive** and a memory semantic supporting **RDMA Read** and **RDMA Write** operations. In the channel semantic, the sending side does not have any information about the receiver's buffer address. It requires a data-structure to be pre-posted at the receiver, so that when the sender sends

its message, it gets stored at the right place in the receiver. If the data-structure is not pre-posted, then the receiver will either send a Receiver Not Ready (RNR) packet to the sender or silently drop the message, depending upon the transport service type such as Reliable Connected and Unreliable Connected. In the memory semantic, one of the following is required for message transfer: the sender is made aware of the receiver's buffer address for RDMA Write or the receiver is made aware of the sender's buffer address for RDMA Read. Typically, this information is exchanged via control messages before an RDMA Write is issued by the sender or an RDMA Read is issued by a receiver. Once the peer's buffer address is known, in RDMA Write, the sender initiates a data transfer to the receiver's buffer. Similarly, in RDMA Read, the receiver initiates a data transfer from the sender's buffer to its local buffer.

In InfiniBand, messages are exchanged over channels that connect the endpoint of one application to the endpoint of any other application or service with which the application needs to communicate. These endpoints are termed as **Queue Pairs** (**QPs**), consisting of one Send Queue and one Receive Queue. Message transfer operations are performed by adding **Work Requests** (**WR**) to these queue pairs. An important field in the WR data structure is the operation code (opcode) which should be set according to the desired operation. Another important group of fields are those that require information about the local or remote memory, which should be set according to the operation. Therefore, in order to create WRs, appropriately-sized memory regions have to be first registered with the **Host Channel Adapter** (**HCA**). For Send/Receive (non RDMA read/write) operations, WRs have to be posted at both sender and receiver, and the information about their local registered memory regions is specified in the WRs. Several of these non-contiguous local memory regions can be associated with one WR by specifying them in an array of data structure called **Scatter-Gather Element** (**SGE**).

When WRs get completed, their completion information is added to a queue called **Completion Queue** (CQ). InfiniBand provides two ways of knowing completions, *event*

notification and polling. By default, event notification is blocking in nature and is interrupt-driven. Also, for event notification, a request has to be first made using the appropriate API call. If a completion happens on the associated CQ, then an interrupt is generated based on the request made by the aforementioned API call. So, in interrupt-driven completion detection, the thread looking for completions simply "sleeps" until it is awoken by an interrupt. The idea behind polling based completion detection is very straightforward. Whenever completion information is required, the associated CQ is polled for completion events. Upon success, the API call returns a list of Work Completions (WC), and an empty list is returned if there are no WCs in the CQ. Note that this call is non-blocking. So, it may have to be called multiple times before the completion of a particular WR is known.

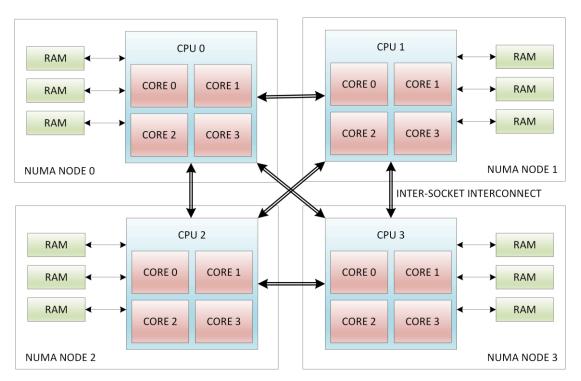

#### 2.1.2 NUMA Based Compute Node

In addition to having multiple compute nodes, each compute node of modern clusters may be equipped with multiple CPUs, with each CPU having several cores. Therefore, intra-node communications may happen between CPU cores and between distinct CPU sockets. A NUMA node (Figure 2.3) consists of a CPU and one or more local memory modules that are directly connected to the CPU's memory controller. A CPU can access the memory of other NUMA nodes by means of a proprietary inter-socket interconnect such as Intel's QuickPath Interconnect [38] and AMD's HyperTransport Technology [4]. Data access across NUMA nodes is slower than accessing the local memory but faster than accessing data on another compute node. Inter-socket communication happens implicitly and is entirely managed by the OS. The application merely has to use an inter-process communication (IPC) mechanism such as shared memory.

Fig. 2.3. Anatomy of a NUMA Compute Node

## 2.1.3 Parallel Programming Paradigms

Fast execution of parallel applications not only requires high performance hardware but also the efficient use of the hardware resources. To achieve this and to relieve the application programmer of dealing with low-level communications and synchronizations, several *parallel programming models* have been developed over the years [6]. A parallel programming model essentially provides an abstraction for the underlying hardware and memory architecture to the application programmer. The memory architecture can be shared or distributed, and modern commodity clusters can support either. Nowadays, the parallel programming models can be implemented on any hardware architecture. However, the choice of a particular programming model for a certain application is not trivial, as the same application can produce different performance results when implemented using different programming models [50].

The existing parallel programming models can be broadly classified into three categories: shared memory, partitioned global address space and distributed memory or message passing. It is, however, possible to employ multiple parallel programming models in a single application. Such a combination of models is referred to as a hybrid model [21]. This chapter provides a brief description about the different parallel programming models and then discusses the different messaging semantics specified in the **Message Passing Interface (MPI)** [54] standard.

## 2.2 Shared Memory Model

The shared memory model can be thread based or non-thread based. In a non-thread based model, each process has access to a common address space to which reads and writes can be performed asynchronously. To avoid race conditions, access to the common address space can be controlled by the use of locks or semaphores. With respect to the shared memory model, a semaphore is a variable that allows a process to have an exclusive access to the common address space for a specific time interval. During this interval the process that has the exclusive access (lock) can manipulate the data in the common address space; whereas the other processes cannot do so until they are granted the lock. This is a simple programming model with no concept of data ownership; hence, any process can access or manipulate the data in the shared memory. On a machine with a shared memory architecture, support for a purely process based shared memory model may be provided natively through the operating system (OS) or through the compiler. On a distributed memory architecture, such a programing model can be supported through specialized hardware or software, for example, Linda [1] and TreadMarks [41].

In the thread based shared memory programming model, instead of executing instructions on multiple heavy-weight processes, each process can spawn multiple light-weight threads which can execute the tasks concurrently. In this model, all the threads of a particular process are associated with a common address space. If there are multiple processes involved; for example, in case of a

hybrid model, the processes themselves may or may not have a common address space. Two popular standards of this model are POSIX Threads or Pthreads [48] and OpenMP [14].

## 2.3 Partitioned Global Address Space Model

In the partitioned global address space (PGAS) model [2], the address space of the entire job is global. The global address space is organized in a data structure such as an array or a cube and each element of this data structure is a dataset. In this model, work is performed by threads that collectively act on the global address space. Each thread has affinity with a partition and it works exclusively on that partition. However, it can access data from other partitions. The threads may also have a private address space and may synchronize among themselves by means of barriers and locks. The important distinction between PGAS and the thread based shared memory model is that in the latter, the shared memory is confined locally to the compute node. However, in PGAS, the local memory can be logically shared across the entire cluster. Two widely used implementations of PGAS are Unified Parallel C (UPC) [23] and Coarray Fortran [58].

## 2.4 Message Passing Model

The message passing model or distributed memory model is the most popular programming model used in HPC [25]. A parallel job executed with this model may consist of several of these processes running on the same physical machine, or span across multiple machines. These processes communicate and synchronize with each other by sending and receiving messages.

The Message Passing Interface [54] is the de-facto standard based on this model. MPICH [55], MVAPICH [56] and OpenMPI [60] are the popular open-source implementations of the MPI standard. These implementations are referred to as middleware as they completely abstract the low-level hardware and communication functions, and expose only the API calls specified in the MPI standard. Most MPI implementations support a variety of networks like InfiniBand [36], iWARP

Ethernet, RoCE and Intel Omni-Path [11]. Also, they are responsible for tasks like process spawning and mapping, setting up connections between the processes and gracefully releasing hardware resources before application termination. The application programmer can simply use the appropriate MPI calls to perform intra-node or inter-node communications.

The MPI standard specifies three types of communication semantics: *two-sided* or *point-to-point communication*, *collective communication* and *one-sided communication* or *Remote Memory Access (RMA)*.

## 2.4.1 Point-to-point Communication

As the name suggests, point-to-point communication involves only a source and a destination. The source and destination can be alternatively called **sender** and **receiver**, respectively. The sending of a message is initiated by the **MPI\_Send** family of calls and the receiving is initiated by the **MPI\_Recv** family of calls. The send requests are matched to the receive requests based on the parameters of **rank**, **tag** and **communicator ID**. The communicator ID or context ID is a handle to a group of processes. Rank specifies the rank of the peer in the specified context ID. The tag parameter can be used to distinguish between multiple messages that involve the same peers in the same communicator. Additionally, the receiver may use wildcards like **MPI\_ANY\_TAG** and/or **MPI\_ANY\_SOURCE** to accept messages with any tag and from any source, respectively.

The sending and receiving MPI calls are available in both *blocking* and *non-blocking* variants. A blocking receive call (MPI\_Recv) will cause the program flow to wait at the call until its expected message has arrived. On the other hand, a blocking send call (MPI\_Send) returns when the local send buffer used for the communication can be reused. In several implementations, this implies that the message has been sent but it does not guarantee the arrival of the message at the destination. In a non-blocking two-sided MPI call (MPI\_Isend/MPI\_Irecv), a request for the send/receive operation is added to the middleware and the task of blocking is deferred to the

**MPI\_Wait** family of calls. The middleware checks for the completion of this request at each blocking call made for other communications and at **MPI\_Test** family of calls. This happens until the communication is complete or until it encounters the request's own MPI\_Wait; at which point, the MPI\_Wait returns immediately if the communication is complete or blocks until completion. The implementation of the blocking and non-blocking point-to-point MPI calls depends largely on the protocol used for communication.

The eager and rendezvous protocols are typically used in the implementations of point-to-point communications. The MPI implementation dynamically decides between these two protocols depending upon the message size. If the message size is below a particular implementation specific threshold then the eager protocol is used; otherwise, the rendezvous protocol is used.

#### **Eager and Rendezvous Protocols**

In the eager protocol, the sender does not require any synchronization with the receiver before sending the user data. The rendezvous protocol on the other hand, requires synchronization between the sender and the receiver by means of control/handshaking messages, before the transfer of the user data is initiated. Eager messages are sent through Send/Receive semantics in InfiniBand or through similar mechanisms in other interconnects. In the rendezvous protocol, the control messages are sent eagerly but the application data is transferred through RDMA Read/Write [76].

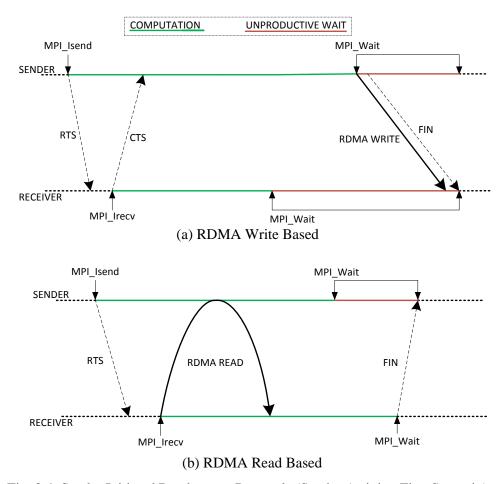

The rendezvous protocol has traditionally been *sender initiated*. A *receiver initiated* rendezvous protocol is possible but is suboptimal compared to the sender initiated protocol. The receiver initiated rendezvous protocol is discussed in depth in the Chapter 3. Figure 2.4 shows the control signals involved in the sender initiated rendezvous protocol. Figure 2.4(a) shows an RDMA Write based implementation of this protocol. As shown in the figure, the communication is initiated by the sender by sending a **Ready to Send (RTS)** control message to the receiver. This message contains the message matching information (rank, tag and context ID), message size and some other

Fig. 2.4. Sender Initiated Rendezvous Protocols (Sender Arriving First Scenario)

implementation specific information. The message matching information is also referred to as the message envelope. Upon arriving at the matching MPI receive call, the receiver replies by sending a **Clear to Send (CTS)** control message. This CTS control message contains the address of the buffer where the data must be written by the sender. At the MPI\_Wait, the sender transfers the user data to the receiver's buffer using RDMA Write and then issues a Finish (FIN) control message to signal the end of the rendezvous communication.

Similarly, Figure 2.4(b) shows an RDMA Read based implementation of the sender initiated rendezvous protocol. As with the RDMA Write based version, the sender initiates the communication by issuing an RTS control message. However, instead of carrying just the message

matching information and message size, this RTS also contains the address of the buffer at the sender where the user data is stored. When the receiver arrives at the matching MPI receive call, it issues an RDMA Read operation to fetch the user data from the remote address specified in the RTS. Finally, at the MPI\_Wait call, the receiver signals the end of the rendezvous communication to the sender through a **FIN** control message. Figure 2.4 represents the scenario where the sender arrives first. If the receiver arrives first, then the task of issuing the CTS/RDMA Read is deferred to MPI\_Wait.

#### **Message Matching and Message Progression**

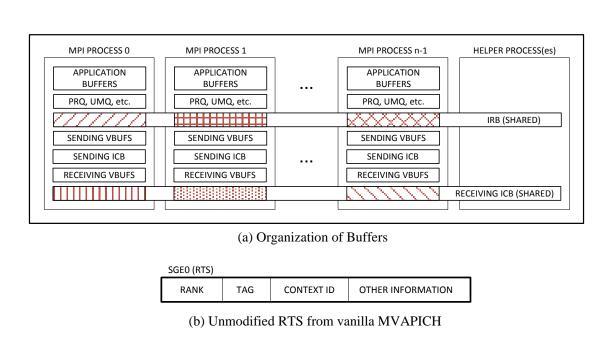

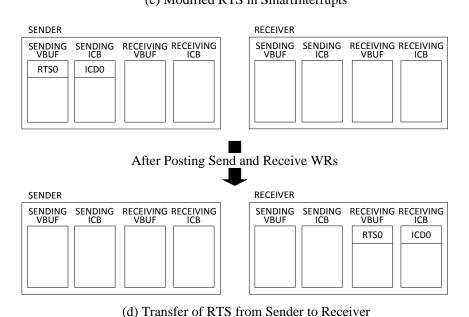

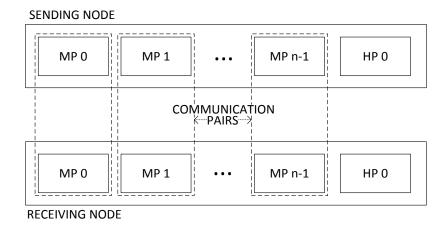

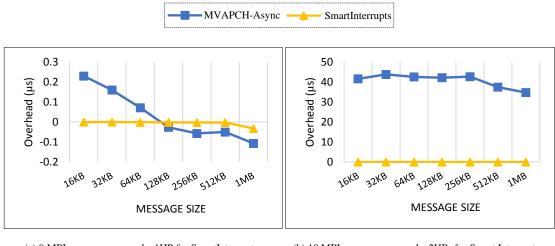

As previously mentioned, eager messages are sent through InfiniBand's Send/Receive semantics. The registered memory region in this case is not the same as the application buffer, which means that the data sent from the sender to the receiver does not land into its ultimate destination directly but instead to an intermediate location. Figure 2.5 shows the hierarchy of buffers in an MPI process. The data needs to be moved from the application buffer of the sender to the application buffer of the receiver. However, it lands intermediately on the communication buffer. This is required for multiple reasons, such as minimizing memory registration costs and providing support for MPI's message-matching semantics. To ensure that the message gets ultimately delivered to the right location, two important operations are employed, *Message Progression* and *Message Matching*. Unexpected Message Queue (UMQ) and Posted Receive Queue (PRQ) are two data structures that support these operations. Transferring a message from the application buffer of one peer to the application buffer of the other peer involves several steps. Such steps may require the copying of the message to intermediate buffers at the middleware or to transfer the message through the wire to the other peer. The execution of one or more of these steps is referred to as message progression. The entity that performs the message progression is often

Fig. 2.5. Hierarchy of Buffers in Common MPI Implementations

referred to as the **progress engine**, and invoked by blocking MPI calls, some non-blocking MPI calls and MPI\_Test family of calls.

Point-to-point MPI receive calls, expecting a message from another process, first invoke message matching to check if their message has already arrived and processed by the progress engine. This is done by first examining the entries of the UMQ to find a match for the expected message. If a match is found, then the rest of the steps are performed according to the protocol followed. Otherwise, a request object is created for that MPI call and added to the PRQ. Messages and requests are said to be matched if their MPI rank, message tag and context ID conform to each other. To find a match for this request object, the progress engine will be called either immediately or at some point in the future. Upon invocation, the progress engine gets a list of WR completions since its last invocation. Among other things, this list contains information about the receive WRs that were completed. At this point, the arrived messages still reside in the registered memory region (the communication buffer). So, message matching is required for further processing. This is done by first comparing the messages with the request objects in the PRQ. If a match is found then the rest of the steps are performed according to the protocol. Otherwise, an entry is added to the UMQ. Note, that a call to the progress engine will progress all the arrived messages in the registered memory region, regardless of the request that it was called for.

One of the tasks of the progress engine is to check for work completions, which it does by calling the appropriate network API functions. As mentioned earlier, InfiniBand provides two ways of knowing completions, event notification by means of interrupts and polling. Consequently, the progress engine can be based on polling or interrupts. In the interrupt based approach, the progress engine sleeps until an interrupt is generated due to a completion on its associated CQ. The progress engine then returns if it finds the message that it was called for; otherwise, goes back to sleep again. The polling based progress engine, on the other hand, calls the completion detection API function several times in a busy loop until the completion of a particular WR is known.

The choice between polling and interrupts requires a careful consideration of the trade-offs. Polling is more responsive than interrupts but it is not as resource efficient. Since polling requires a continuous examination of the CQs in a busy loop, the progress engine inflicts a 100 percent CPU utilization on the core on which it is mapped. In contrast, an interrupt based progress engine essentially sleeps until a completion, so its CPU utilization during that time is zero. Polling does not require any interaction with the kernel and no context-switching is involved either. However, interrupts are associated with interrupt-generation and context-switching overheads, that make them less responsive compared to polling.

## **Communication/Computation Overlap**

As mentioned earlier, with RDMA, the communication is entirely offloaded to the NIC and the CPU only has to be involved for a very short duration to add a communication request to the NIC. This provides the ability to hide the latency of the communications by overlapping it with the computations. The semantics of blocking point-to-point MPI calls depends a lot on the type of the call (send/receive) and on the protocol used. In general, blocking MPI calls have to wait until the message is progressed partly or completely. This wait becomes even more severe with rendezvous protocols because of the size of the messages and the involvement of control signals. During this

wait, the CPU is basically wasting CPU cycles as the communication is being carried out by the NIC. Also, while the blocking call is waiting for its message to be progressed, the application thread obviously cannot proceed with the computation. Therefore, the use of blocking two-sided calls may cause the communication and computation to get serialized; although, this cannot be avoided in some circumstances. On the other hand, non-blocking calls perform the necessary actions and return immediately. If an expected message is not found then instead of waiting for it, a non-blocking call adds a communication request at the middleware and delegates the task of message progression to the future progress engine calls. After issuing the non-blocking call, the application can immediately proceed to other activities. This promotes communication/computation overlap by deferring the communication to a more opportune time, and sneaking in computation in the meantime. Therefore, the use of non-blocking calls facilitates the overlap of communication and computation.

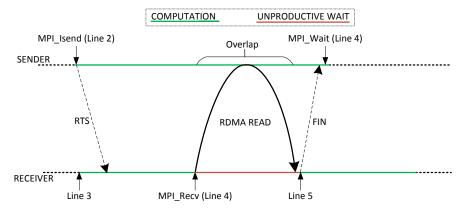

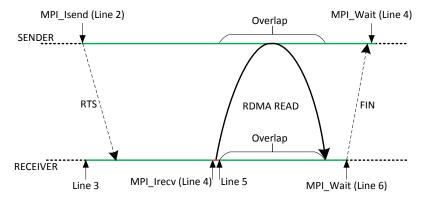

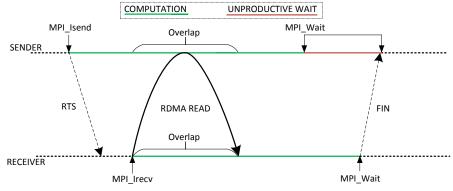

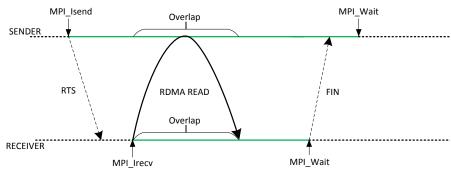

Figure 2.6 illustrates two code snippets that implement the same logic using blocking and non-blocking receive calls, and compares their communication/computation overlap. In this figure, assume that the message is larger than the eager threshold and that the sender initiated RDMA Read based rendezvous protocol is used. This section aims to explain the concept of communication/computation overlap in two-sided communication, therefore, it uses a very specific example. For the same reason, this discussion is limited to the receiver side overlap. A detailed discussion on the overlap in other scenarios and other rendezvous protocols can be found in Chapter 3.

The sender and receiver in both the code snippets start with the MPI\_Barrier to ensure that line 2 starts at almost the same time in both the peers. Since the focus is on the receiver side overlap, the sender simply issues the non-blocking send call, performs its computation and issues the MPI\_Wait call to wait until the communication is complete. The receiver's code in Figure 2.6(a) performs some computation, then issues a blocking receive (MPI\_Recv) and continues with its computation. The receiver's code in Figure 2.6(c) performs essentially the same actions but

replaces the MPI\_Recv with its non-blocking version (MPI\_Irecv) and adds an MPI\_Wait after the second computation. Note, that in both the receiver snippets, the execution durations of the instrumentation functions at line 2 and line 6/line 7 are negligible compared to the other statements, hence their contribution to the total elapsed time can be ignored. As shown in Figure 2.6(b), the MPI\_Recv does not return until the entire message is progressed. This is because it cannot send the Finish (FIN) control message until the RDMA Read is compete. Therefore, the result is a strict serialization of communication and computation. On the other hand, with MPI\_Irecv, the RDMA Read overlaps with the computation at line 5. The RTS is already present at the receiver when the MPI\_Irecv gets called, so the receiver issues the RDMA Read and continues with its computation. The MPI\_Irecv is paired with the MPI\_Wait at line 6, which would have ultimately blocked if the communication had not been progressed. In this case, however, the only task left for it is to send the FIN control signal. With same computations and message size, the two code snippets would perform exactly the same task, however, the lack of overlap with the blocking receive would cause the elapsed time to be greater.

## 2.4.2 Collective Communications

Along with performing communications between pairs of MPI processes, the MPI standard provides the provision of involving multiple processes in a communication through MPI collectives. The standard specifies collectives for communications such as: sending the same data from one process to the others (MPI\_Bcast), distributing chunks of data from one process to the others (MPI\_Scatter), gathering data from different processes to a single process (MPI\_Gather), performing a reduction operation on numeric data supplied by the participating processes (MPI\_Reduce), etc. Similar to point-to-point MPI calls, collectives are available in both blocking and non-blocking variants. At the middleware, collectives may be implemented using two-sided MPI calls [77] or one-sided MPI calls [79], or using special network API calls that are optimized

# SENDER: 1. MPI\_Barrier(MPI\_COMM\_WORLD) 2. MPI\_Isend 3. Computation 4. MPI\_Wait 4. MPI\_Wait 4. MPI\_Wait 5. Computation 6. Meaure stop\_time 7. elapsed\_time = stop\_time - start time

## (a) Code Snippet with Blocking Receive Call (MPI\_Recv)

## (b) Timing Diagram for (a)

## (c) Code Snippet with Non-Blocking Receive Call (MPI\_Irecv + MPI\_Wait)

(d) Timing Diagram for (c)

Fig. 2.6. Comparison of Communication/Computation Overlap between Blocking and Non-Blocking

Two-Sided Calls in RDMA Read Rendezvous Protocol

for collectives [32, 37]. Therefore, the message progression semantics of a collective communication would be similar to that of the implementation on which it is based.

## 2.4.3 One-Sided Communication

One-sided communication was introduced in the version 2.0 of the MPI standard and has undergone significant revisions in version 2.2 and version 3.0. It is not as widely used in scientific applications as two-sided communication [15], but is known to have lower latencies for large messages [40]. Unlike two-sided communication, in one-sided communication, data can be moved to or fetched from a remote process without requiring any synchronization with the remote process. Also, the remote process does not have to issue a matching API call to initiate the data transfer, unlike two-sided communication. Communications are done by directly performing operations on the exposed region of the remote process's memory. Hence, one-sided communication is also referred to as Remote Memory Access (RMA). In RMA terminology, the exposed remote buffer is called a window. The remote process is called the target and the process that performs operations on the window of the target is called the **origin**. Before starting the RMA operations, all the involved peers call the MPI\_Win\_create function. MPI\_Win\_create is a collective call that returns a window object which can be used by these processes to perform RMA operations. Each process may specify a window of its local memory that it intends to expose to RMA accesses by the other processes in the group. Alternatively, a process may elect to expose no memory by specifying a window size of zero.

The MPI standard specifies three types of RMA operations: MPI\_Put to transfer data from the origin to the target, MPI\_Get to transfer data from the target to the origin and MPI\_Accumulate to perform a remote arithmetic operation. These operations do not require target-origin synchronizations; however, RMA as a whole is not synchronization free. In MPI, the RMA synchronizations can be of the following two types, namely, active target and passive target.

## **Active Target Synchronization**

In active target, synchronization between the targets and origins is required at two stages. The duration between these stages is the period for which a window remains exposed for RMA operations, and is referred to as the *epoch*. In the first stage, an epoch starting call is required among the peers to exchange window exposure information. Then, after all RMA operations are performed on the window, an epoch completing function is called to signal that the window is no longer required to be exposed. A target window can be accessed by RMA operations only within an *exposure epoch*. Such an epoch is started and completed by RMA synchronization calls executed by the target process. Similarly, RMA synchronization calls are executed by the origin to start and complete an *access epoch*, during which it may issue RMA operations to the target's window.