# High-Performance Interconnect-Aware MPI communication for Deep Learning Workloads

## Yıltan Hassan Temuçin

A thesis submitted to the Department of Electrical and Computer Engineering in conformity with the requirements for the degree of Master of Applied Science

Queen's University

Kingston, Ontario, Canada

November 2021

Copyright © Yıltan Hassan Temuçin, 2021

# Abstract

High-Performance Computing (HPC) refers to using aggregate compute power of many small compute nodes to solve large complex problems which cannot be computed in a reasonable time on a single computer. In recent years these HPC clusters have moved towards using accelerators, such as Graphics Processing Units (GPUs), to offload computationally intensive portions of applications. Distributed Deep Learning workloads on these heterogeneous HPC systems has become increasingly important. These new workloads have been developed upon existing HPC libraries such as the Message Passing Interface (MPI) and Compute Unified Device Architecture (CUDA).

MPI communication is critical to distributed Deep Learning applications at scale as they place a large amount of pressure on the communication subsystem of HPC clusters. Improving the MPI communication run-time could benefit Deep Learning. For that, we first investigate the characteristics of Deep Learning applications to understand how we can propose and design communication mechanisms which solve some important communication challenges.

We focused on tackling the issues regarding large GPU messages, which we observed with Deep Learning applications. To begin our investigation, we studied NVLink usage within the context of point-to-point communication. Unified Communication X (UCX) framework, used within the Open MPI library, only utilises a small portion of the available NVLink bandwidth for intra-socket GPU-to-GPU

communication. We propose a novel GPU-to-GPU data transfer mechanism that stripes the message across multiple intra-socket communication channels and multiple memory regions using multiple GPU streams to utilise all available NVLink paths. Our approach achieves 1.64x and 1.84x higher bandwidth for both UCX and Open MPI + UCX, respectively.

Then we propose a 3-stage hierarchical, pipelined MPI\_Allreduce design that incorporates the new multi-path NVLink data transfer mechanism for intra-socket communication in the first and third stages of the collective, and PCIe and X-bus channels for inter-socket GPU-to-GPU communication in the second stage with minimal interference. For large messages, our proposed algorithm achieves a large speedup.

Finally, we evaluate our proposed MPI\_Allreduce for Deep Learning applications such as Horovod + TensorFlow with a range of Deep Learning models. For Horovod + TensorFlow and VGG16, we observe up to 3.42x speedup over other MPI implementations.

# Statement of Collaboration

The work in Chapter 3 was completed collaboratively with Pedram Alizadeh. In Chapter 3, Pedram Alizadeh and I worked on the design of the profiler. Joint decisions were made on which metrics should be gathered and their importance. The PMPI profiler code was solely written by myself, as well as any data processing presented in this thesis.

In Chapter 4, AmirHossein Sojoodi and I collaboratively wrote code which showed that the multi-path copy was viable on the Mist compute node. This code was for a single process using multiple GPUs outside of the MPI library. The related results are not present in my thesis as that idea was extended to a multi-process environment and implemented inside UCX.

In Chapter 5, Pedram Alizadeh first mentioned the benefits of using a three stage algorithm and how that could potentially allow us to use the multi-path copy feature within the context of MPI\_Allreduce. The design and implementation of the algorithm and the additional extensions, which are discussed in the thesis, was done by myself.

# Acknowledgements

I would like to thank my supervisor Professor Ahmad Afsahi for his guidance and support during this thesis. His passion and his pursuit for extending research in new directions has certainly helped me learn the complexity of research and what I am capable of. I would also like to acknowledge the Electrical and Computer Engineering (ECE) Department for their financial support through Teaching Assistantship, Queen's University for the Queen's Graduate Award (QGA), and The Natural Science and Engineering Research Council of Canada through Graduate Research Fellowships (GRF). Finally, I would like to thank Compute Canada for providing access to the Béluga, Cedar, and Mist compute clusters, as well as Fei Mao and Bruno C. Mundim at SciNet for their technical support on Mist.

Many thanks to my colleagues and friends at the Parallel Processing Research Laboratory; Dr. Mahdieh Ghazimirsaeeed, Pedram Alizadeh, Leila Habibpour Tanyani, AmirHossein Sojoodi, and Benjamin Kitor. Special thanks towards Pedram Alizadeh and AmirHossein Sojoodi for their collaboration during my thesis. I look forward to developing all these relationships both as friends and professionally as I start my PhD.

I appreciate my housemate Avi and his patience with me as we transitioned to working from home this past year. Lastly, I would like to thank my parents, Altan and Özlem, and my brother Ertan for their support during this period.

# Contents

| Α            | bstra       | act                   | i   |

|--------------|-------------|-----------------------|-----|

| St           | aten        | nent of Collaboration | iii |

| $\mathbf{A}$ | ckno        | wledgements           | iv  |

| Ta           | able        | of Contents           | v   |

| ${f Li}$     | st of       | Algorithms            | ix  |

| Li           | ${f st}$ of | Figures               | х   |

| Li           | ${f st}$ of | Tables                | xiv |

| Li           | ${f st}$ of | Code Listings         | xv  |

| $\mathbf{G}$ | lossa       | ry                    | xvi |

| 1            | Inti        | roduction             | 1   |

|              | 1.1         | Motivation            | 2   |

|              | 1.2         | Research Objectives   | 3   |

|              | 1.3         | Contributions         | 4   |

|              | 1.4         | Outline               | 6   |

| <b>2</b>     | Bac         | ckground              | 7   |

CONTENTS

|   | 2.1 | Moder   | rn Heterogeneous HPC Clusters                            | 8   |

|---|-----|---------|----------------------------------------------------------|-----|

|   | 2.2 | Graph   | ics Processing Units (GPUs)                              | 9   |

|   |     | 2.2.1   | GPU Architecture                                         | 10  |

|   |     | 2.2.2   | Programming Nvidia GPUs                                  | 10  |

|   | 2.3 | Netwo   | ork Interconnects                                        | 11  |

|   |     | 2.3.1   | PCIe                                                     | 12  |

|   |     | 2.3.2   | NVLink                                                   | 12  |

|   |     | 2.3.3   | InfiniBand                                               | 12  |

|   | 2.4 | The M   | Message Passing Interface (MPI)                          | 13  |

|   |     | 2.4.1   | Point-To-Point Communication                             | 14  |

|   |     | 2.4.2   | Collective Communication                                 | 15  |

|   |     | 2.4.3   | GPU-Aware MPI                                            | 21  |

|   |     | 2.4.4   | MPI Implementations                                      | 21  |

|   | 2.5 | Distril | buted Deep Learning                                      | 24  |

|   |     | 2.5.1   | Distributed Training                                     | 24  |

|   |     | 2.5.2   | Deep Learning Frameworks                                 | 26  |

| 3 | Con | nmuni   | cation Characterisation of Distributed Deep Learning Fra | me- |

|   | wor | ks      |                                                          | 29  |

|   | 3.1 | Relate  | ed Work                                                  | 30  |

|   | 3.2 | Motiva  | ation                                                    | 32  |

|   | 3.3 | Dynar   | nic Analysis of Deep Learning Frameworks                 | 33  |

|   |     | 3.3.1   | Experimental Setup                                       | 33  |

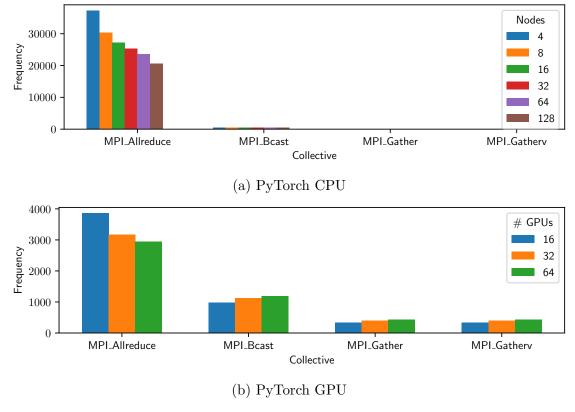

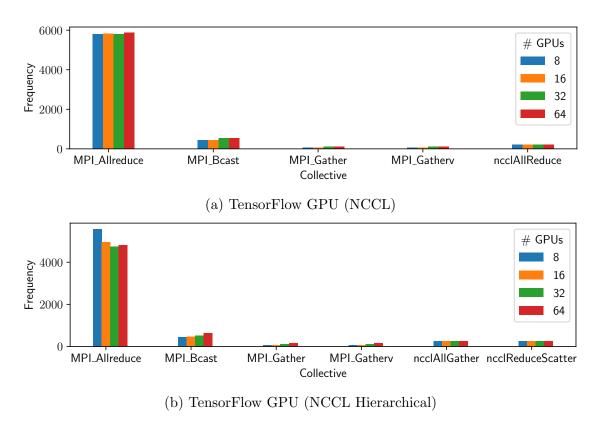

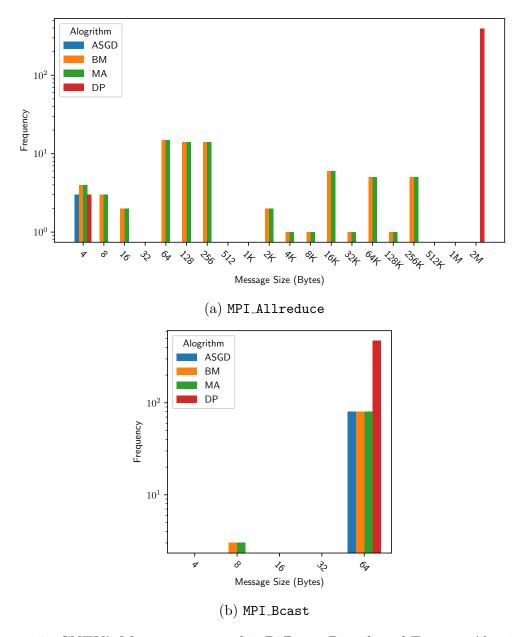

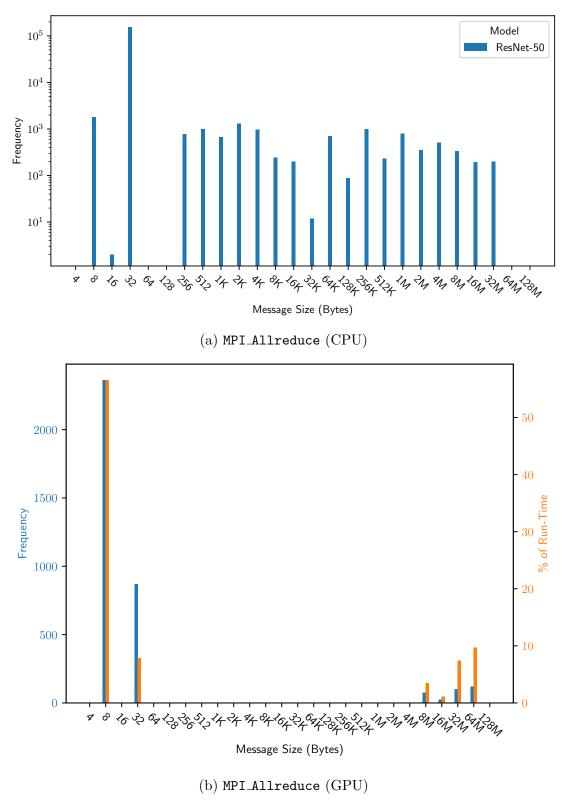

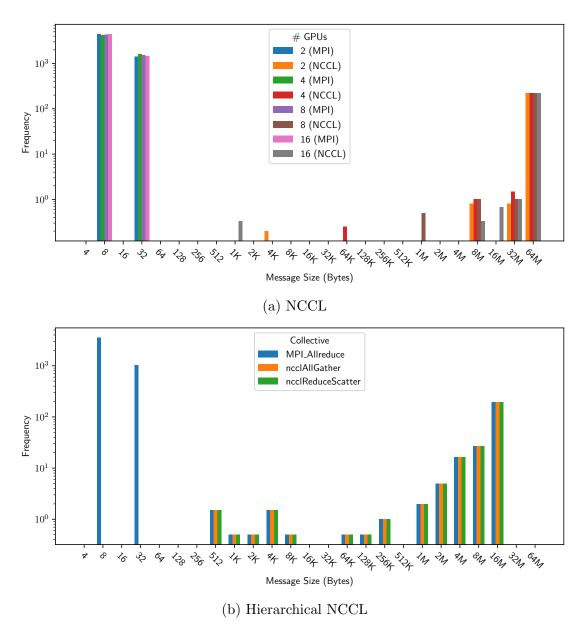

|   |     | 3.3.2   | Frequency of MPI API calls                               | 35  |

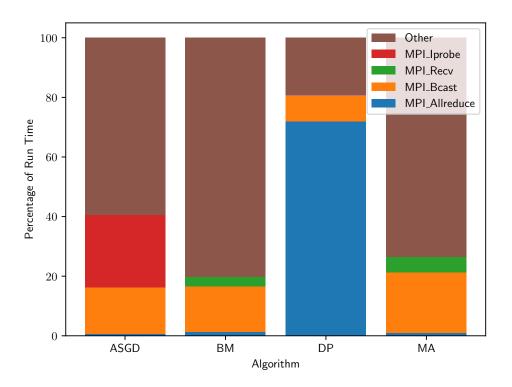

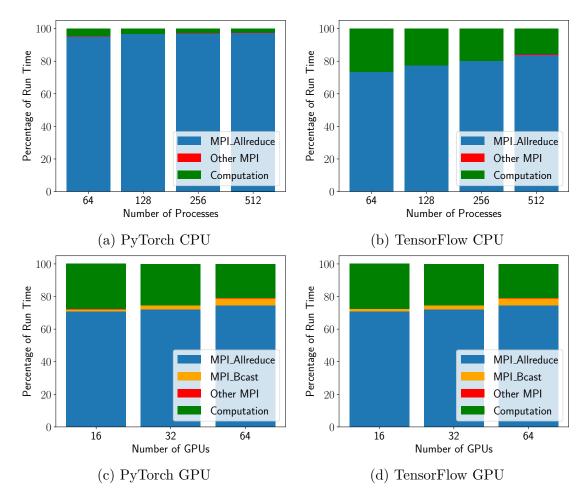

|   |     | 3.3.3   | Impact of MPI Communication on Application Time          | 40  |

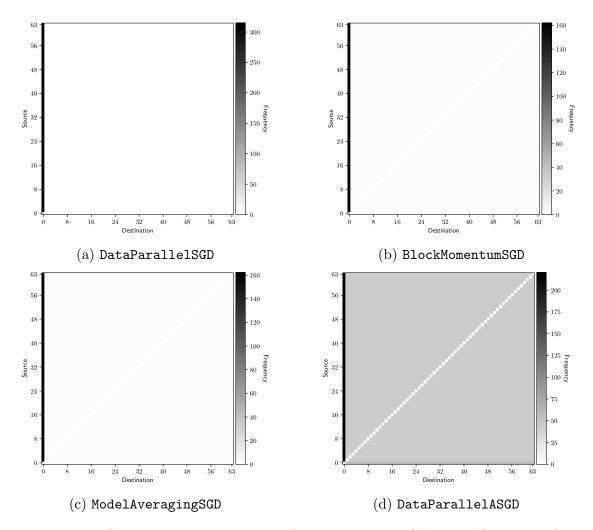

|   |     | 3.3.4   | Message Sizes used by Collectives                        | 43  |

|   |     | 3.3.5   | Point-To-Point Communication Pattern                     | 50  |

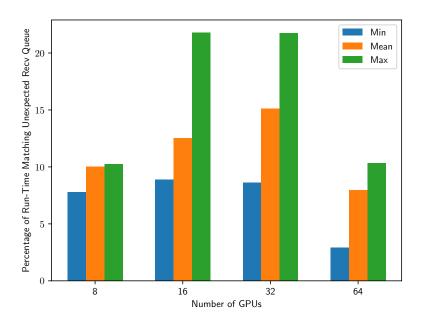

|   |     | 3.3.6   | MPI Message Queues                                       | 51  |

CONTENTS

|   | 3.4                                           | Summ                                                                                       | ary                                                                                                                                                                                                                                                                         | 52                                                 |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 4 | Mu                                            | lti-Pat                                                                                    | h Point-to-Point GPU Communication                                                                                                                                                                                                                                          | <b>54</b>                                          |

|   | 4.1                                           | Relate                                                                                     | d Work                                                                                                                                                                                                                                                                      | 55                                                 |

|   | 4.2                                           | Motiva                                                                                     | ation                                                                                                                                                                                                                                                                       | 56                                                 |

|   | 4.3                                           | Design                                                                                     | and Implementation                                                                                                                                                                                                                                                          | 58                                                 |

|   |                                               | 4.3.1                                                                                      | Host Staged Data Transfers                                                                                                                                                                                                                                                  | 59                                                 |

|   |                                               | 4.3.2                                                                                      | Using Multiple Paths - Host Staged and Device To Device                                                                                                                                                                                                                     |                                                    |

|   |                                               |                                                                                            | Copies                                                                                                                                                                                                                                                                      | 60                                                 |

|   | 4.4                                           | Perfor                                                                                     | mance Evaluation and Analysis                                                                                                                                                                                                                                               | 61                                                 |

|   |                                               | 4.4.1                                                                                      | Experimental Setup                                                                                                                                                                                                                                                          | 62                                                 |

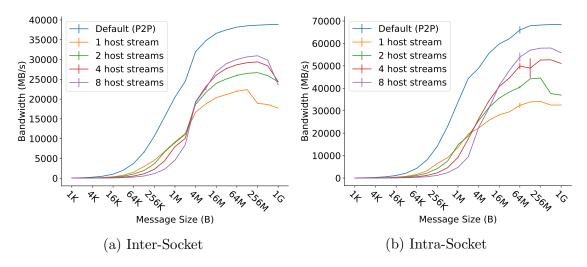

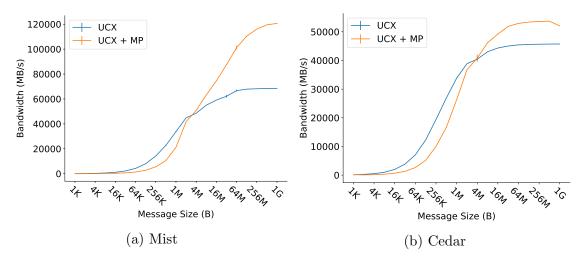

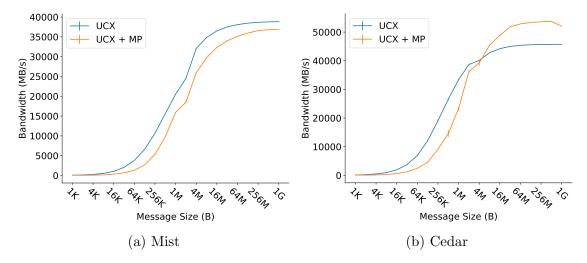

|   |                                               | 4.4.2                                                                                      | UCX Put Results                                                                                                                                                                                                                                                             | 62                                                 |

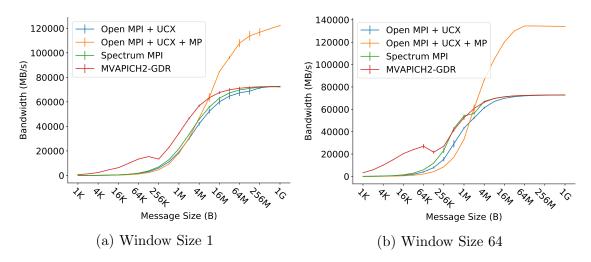

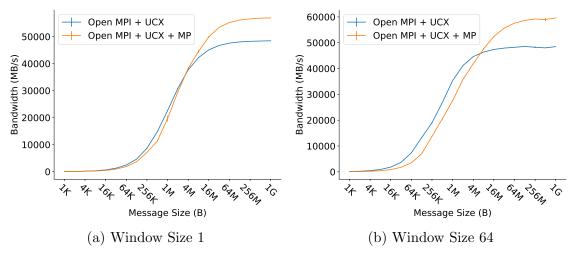

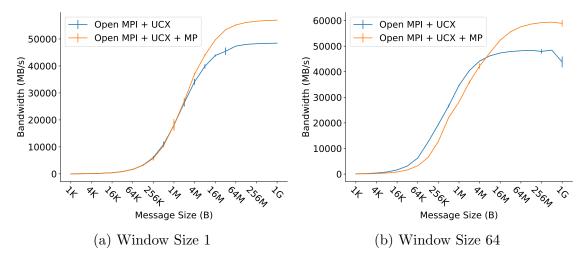

|   |                                               | 4.4.3                                                                                      | MPI Point-to-Point Results                                                                                                                                                                                                                                                  | 65                                                 |

|   | 4.5                                           | Summ                                                                                       | ary                                                                                                                                                                                                                                                                         | 70                                                 |

|   |                                               |                                                                                            |                                                                                                                                                                                                                                                                             |                                                    |

| 5 | GP                                            | U-Awa                                                                                      | ${f re}$ MPI_Allreduce ${f Design}$                                                                                                                                                                                                                                         | <b>71</b>                                          |

| 5 | <b>GP</b> <sup>7</sup> 5.1                    |                                                                                            | are MPI_Allreduce <b>Design</b>                                                                                                                                                                                                                                             | <b>71</b> 72                                       |

| 5 |                                               | Relate                                                                                     | <u> </u>                                                                                                                                                                                                                                                                    |                                                    |

| 5 | 5.1                                           | Relate<br>Motiva                                                                           | d Work                                                                                                                                                                                                                                                                      | 72                                                 |

| 5 | 5.1<br>5.2                                    | Relate<br>Motiva                                                                           | d Work                                                                                                                                                                                                                                                                      | 72<br>73                                           |

| 5 | 5.1<br>5.2                                    | Relate<br>Motiva<br>Design                                                                 | d Work                                                                                                                                                                                                                                                                      | 72<br>73<br>74<br>75                               |

| 5 | 5.1<br>5.2                                    | Relate<br>Motiva<br>Design<br>5.3.1                                                        | d Work                                                                                                                                                                                                                                                                      | 72<br>73<br>74<br>75<br>78                         |

| 5 | 5.1<br>5.2                                    | Relate Motiva Design 5.3.1 5.3.2 5.3.3                                                     | d Work                                                                                                                                                                                                                                                                      | 72<br>73<br>74<br>75                               |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Relate Motiva Design 5.3.1 5.3.2 5.3.3                                                     | d Work                                                                                                                                                                                                                                                                      | 72<br>73<br>74<br>75<br>78<br>79                   |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Relate<br>Motiva<br>Design<br>5.3.1<br>5.3.2<br>5.3.3<br>Perfor                            | d Work  ation                                                                                                                                                                                                                                                               | 72<br>73<br>74<br>75<br>78<br>79<br>82             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Relate<br>Motiva<br>Design<br>5.3.1<br>5.3.2<br>5.3.3<br>Perfor<br>5.4.1                   | d Work  ation  and Implementation  MPI_Allreduce with GPU Kernel Reduction  MPI_Allreduce with GPU Kernel Reduction with Tuning Table  Proposed Hierarchical MPI_Allreduce with Multi-Path Copy  mance Evaluation and Analysis  Experimental Setup                          | 72<br>73<br>74<br>75<br>78<br>79<br>82<br>82       |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Relate<br>Motiva<br>Design<br>5.3.1<br>5.3.2<br>5.3.3<br>Perfor<br>5.4.1<br>5.4.2<br>5.4.3 | d Work  ation  and Implementation  MPI_Allreduce with GPU Kernel Reduction  MPI_Allreduce with GPU Kernel Reduction with Tuning Table  Proposed Hierarchical MPI_Allreduce with Multi-Path Copy  mance Evaluation and Analysis  Experimental Setup  Micro-Benchmark Results | 72<br>73<br>74<br>75<br>78<br>79<br>82<br>82<br>82 |

| CONTENTS |             |    |

|----------|-------------|----|

| 6.1      | Conclusion  | 95 |

| 6.2      | Future Work | 98 |

| Bibliog  | graphy 1    | 00 |

# List of Algorithms

| 4.1 | Multi-Path Copy Algorithm  |                                | 6. |

|-----|----------------------------|--------------------------------|----|

| 5.1 | Hierarchical MPI_Allreduce | with Multi-Path Copy Algorithm | 81 |

# List of Figures

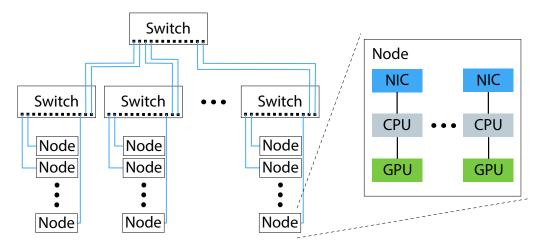

| 2.1  | Schematic diagram of a modern heterogeneous HPC cluster                  | 9  |

|------|--------------------------------------------------------------------------|----|

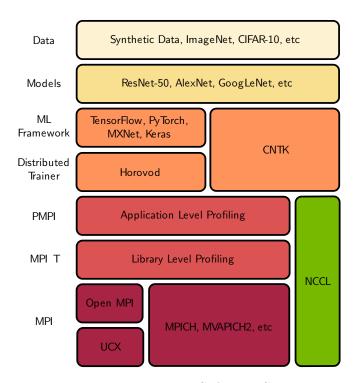

| 2.2  | Software Stack                                                           | 13 |

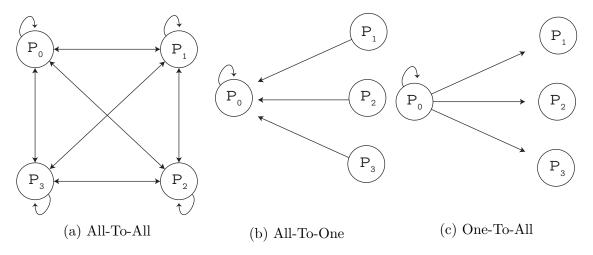

| 2.3  | Different MPI Collective Communication Patterns                          | 15 |

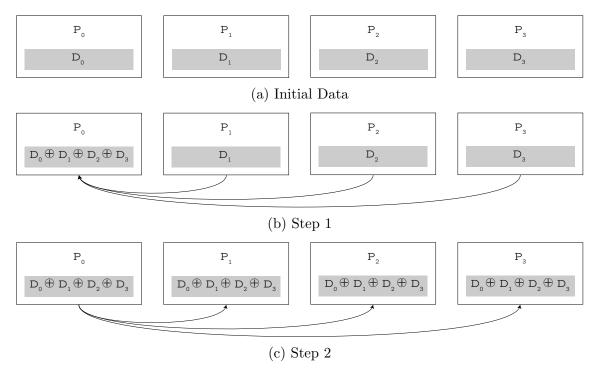

| 2.4  | MPI_Allreduce Reduce-Broadcast algorithm for 4 processes                 | 17 |

| 2.5  | MPI_Allreduce Recursive Doubling algorithm for 4 processes               | 18 |

| 2.6  | MPI_Allreduce RSA algorithm for 4 processes                              | 19 |

| 2.7  | MPI_Allreduce Ring algorithm for 4 processes                             | 20 |

| 2.8  | Simplified Software Stack of Open MPI + UCX $\ \ldots \ \ldots \ \ldots$ | 23 |

| 2.9  | Schematic diagram of distributed training using data parallelism         | 25 |

| 2.10 | Schematic diagram displaying an example of model parallelism using       |    |

|      | 4 processes                                                              | 26 |

| 3.1  | Frequency of MPI calls used in different configurations of CNTK for      |    |

|      | ResNet-20                                                                | 36 |

| 3.2  | Frequency of MPI collectives used in CPU and GPU configurations          |    |

|      | of Horovod + TensorFlow for ResNet-50                                    | 38 |

| 3.3  | Frequency of MPI collectives used in the CPU and GPU configura-          |    |

|      | tions of Horovod + PyTorch for ResNet-50                                 | 38 |

| 3.4  | Frequency of MPI and NCCL collectives used in the NCCL configu-          |    |

|      | rations of Horovod + TensorFlow for ResNet-50                            | 39 |

| 3.5  | Percentage of Run-Time Spent in MPI for CNTK's Training Methods          | 40 |

| 3.6  | Impact of MPI Communication on Application Run-Time for Differ-         |

|------|-------------------------------------------------------------------------|

|      | ent Process Counts of Horovod using ResNet-50                           |

| 3.7  | CNTK's Message sizes used in Different Distributed Training Algo-       |

|      | rithms for ResNet-20 with CIFAR-10                                      |

| 3.8  | Message sizes used by different collectives in PyTorch for CPU and      |

|      | GPU configurations                                                      |

| 3.9  | Message sizes used by different collectives in TensorFlow for CPU and   |

|      | GPU configurations                                                      |

| 3.10 | Message sizes used by AllReduce for different NCCL configuration for    |

|      | TensorFlow training ResNet50                                            |

| 3.11 | Communication Partners of Point-To-Point Calls in different config-     |

|      | urations of CNTK for ResNet-20                                          |

| 3.12 | Percentage of Run-Time Spent Matching Unexpected Recv Queue for         |

|      | ResNet-20 using DataParallelASGD                                        |

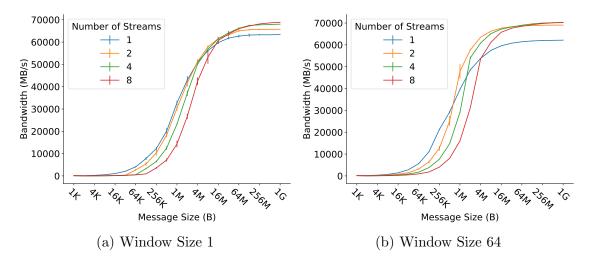

| 4.1  | UCX Put bandwidth measurement taken using ucx_perftest. Using           |

|      | peer copies is compared to using host staged copies with a different    |

|      | number of streams. Results from Mist are shown                          |

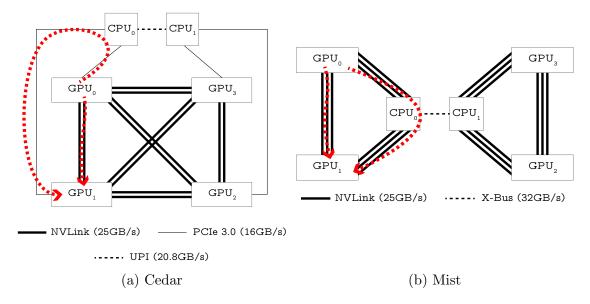

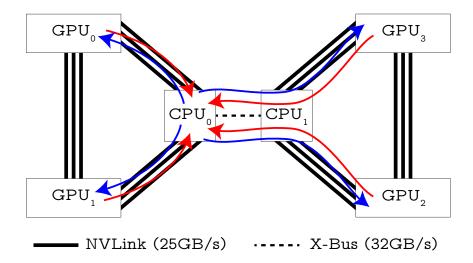

| 4.2  | Single node physical typologies of Compute Canada systems. Uni-         |

|      | directional bandwidth is labelled for each system. The path of the      |

|      | multi-path copies are shown in red                                      |

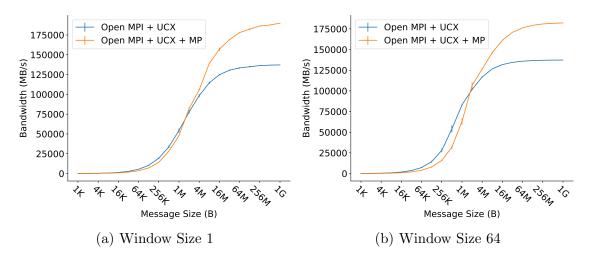

| 4.3  | Intra-Socket UCX Put bandwidth measurement taken using ucx_perftest. 64 |

| 4.4  | Inter-Socket UCX Put bandwidth measurement taken using ucx_perftest. 64 |

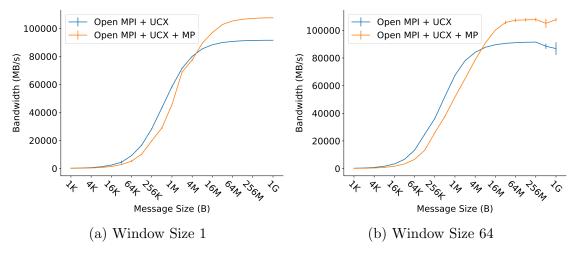

| 4.5  | Intra-socket uni-directional bandwidth measurement taken using OMB      |

|      | on Mist                                                                 |

| 4.6  | Intra-socket uni-directional bandwidth measurement taken using OMB      |

|      | on Cedar                                                                |

| 4.7  | Inter-socket uni-directional bandwidth measurement taken using ${\rm OMB}$ |    |

|------|----------------------------------------------------------------------------|----|

|      | on Cedar                                                                   | 67 |

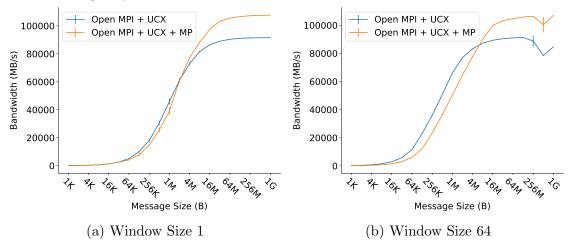

| 4.8  | Intra-socket bi-directional bandwidth measurement taken using OMB          |    |

|      | on Mist                                                                    | 68 |

| 4.9  | Intra-socket bi-directional bandwidth measurement taken using OMB          |    |

|      | on Cedar                                                                   | 68 |

| 4.10 | Intra-socket bi-directional bandwidth measurement taken using OMB          |    |

|      | on Mist using only the NVLinks connected to the host                       | 69 |

| 4.11 | Inter-socket bi-directional bandwidth measurement taken using OMB          |    |

|      | on Cedar                                                                   | 69 |

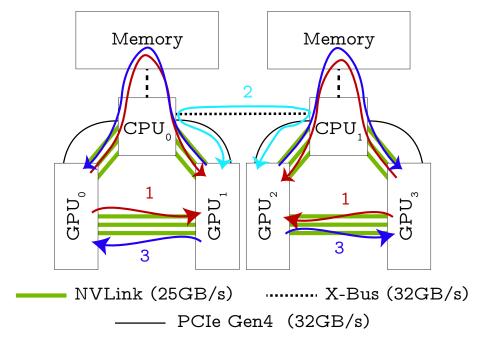

| 5.1  | Single node physical topology of SciNet system Mist. Uni-directional       |    |

|      | bandwidth is labelled for each interconnect. Red arrow shows the           |    |

|      | first step of of copying the data from D2H in the Open MPI imple-          |    |

|      | mentation of MPI_Allreduce. The CPU based reduction occurs using           |    |

|      | the appropriate collective algorithm. Then the blue arrow shows the        |    |

|      | second step copy the data from H2D                                         | 74 |

| 5.2  | Physical topology of Mist with our proposed algorithm overlaid. Uni-       |    |

|      | directional bandwidth is labelled for each interconnect                    | 79 |

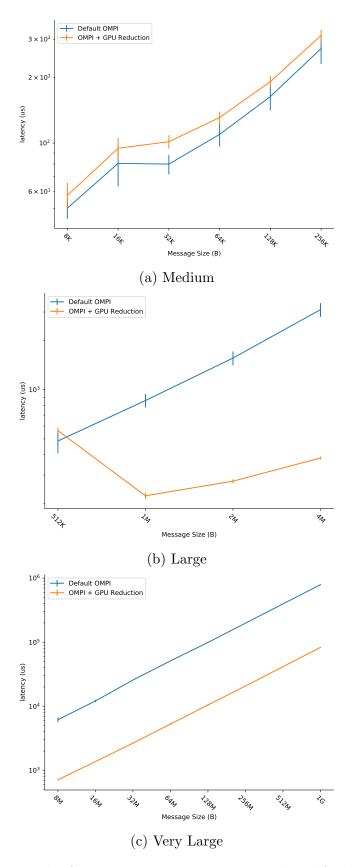

| 5.3  | OMB results for MPI_Allreduce comparing the default Open MPI               |    |

|      | implementation with a CPU reduction to our GPU kernel based re-            |    |

|      | duction design on Mist                                                     | 83 |

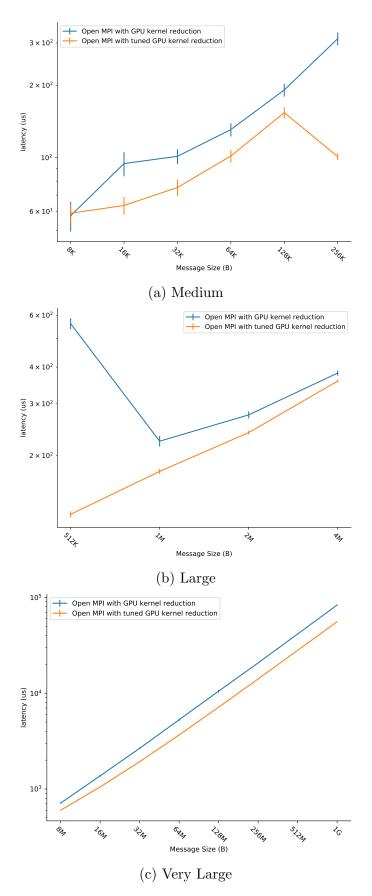

| 5.4  | OMB results for MPI_Allreduce comparing the GPU kernel based               |    |

|      | reduction design with and without a algorithm tuning table on Mist.        | 85 |

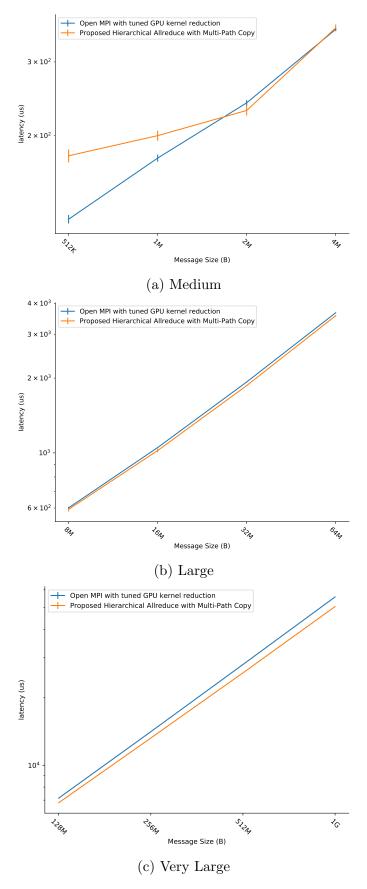

| 5.5  | OMB results for MPI_Allreduce comparing the tuned GPU kernel               |    |

|      | based reduction design with our proposed algorithm on Mist                 | 87 |

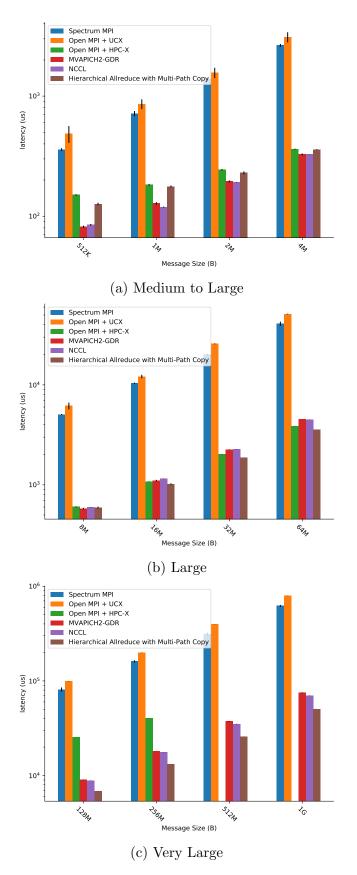

| 5.6 | MPI_Allreduce results comparing our proposed hierarchical allreduce                                 |    |

|-----|-----------------------------------------------------------------------------------------------------|----|

|     | with multi-path copy against Spectrum MPI, Open MPI + UCX,                                          |    |

|     | Open MPI + HPC-X, MVAPICH2-GDR, and NCCL on Mist $\ \ .$                                            | 89 |

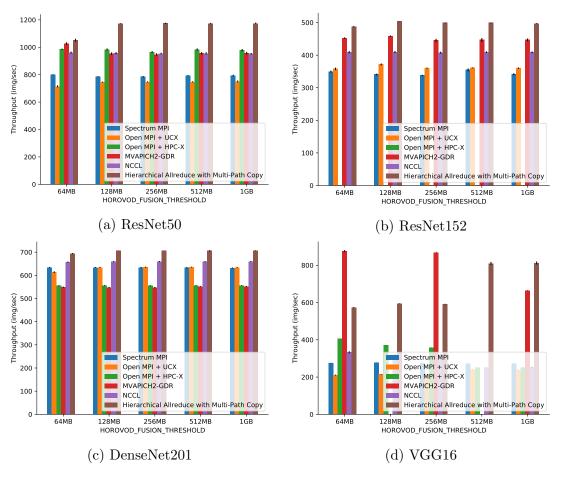

| 5.7 | ${\bf Horovod + TensorFlow\ throughput\ with\ different\ models,\ a\ batch\ size}$                  |    |

|     | of 32, and different values of HOROVOD_FUSION_THRESHOLD for each                                    |    |

|     | MPI implementation and NCCL on Mist                                                                 | 90 |

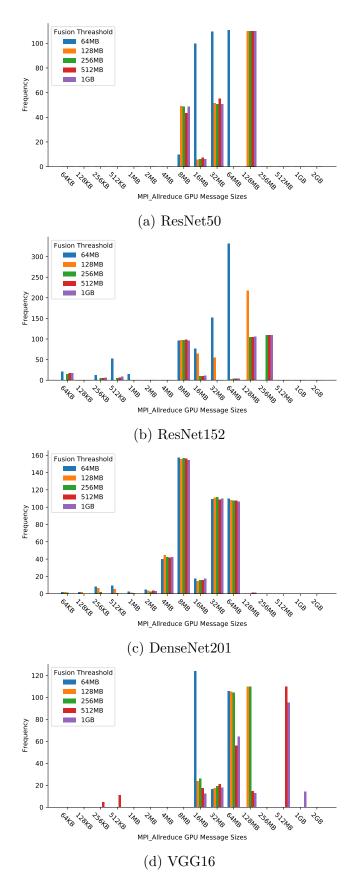

| 5.8 | $\label{thm:message} Message\ sizes\ used\ by\ {\tt MPI\_Allreduce}\ for\ Horovod+TensorFlow\ with$ |    |

|     | different models, a batch size of 32, and <code>HOROVOD_FUSION_THRESHOLD</code>                     |    |

|     | on Mist                                                                                             | 92 |

# List of Tables

| 3.1 | Percentage of Run-time Spent in Communication for ResNet50 on 64      |    |

|-----|-----------------------------------------------------------------------|----|

|     | GPUs using Horovod + TensorFlow                                       | 43 |

| 3.2 | Throughput for ResNet50 on 64 GPUs using Horovod $+$ TensorFlow       | 43 |

| 4.1 | Example Tuning Table for Optimising UCX Put Bandwidth Results         |    |

|     | for Intra-Socket Multi-Path Transfers. For brevity only messages from |    |

|     | 1M-1G is shown. All values were obtained but we only see perfor-      |    |

|     | mance improvement around the 1M mark                                  | 63 |

| 5.1 | Tuning Table for the proposed algorithm                               | 82 |

# List of Code Listings

| 4.1 | Opening CUDA IPC Memory Handle Pseudo-code          | 60 |

|-----|-----------------------------------------------------|----|

| 5.1 | Buffer Location Allocation Logic                    | 76 |

| 5.2 | Lazy Buffer Allocation Logic                        | 76 |

| 5.3 | Kernel reduction for MPI_FLOAT and MPI_SUM use case | 77 |

# Glossary

**ASIC** An ASIC is an Application Specific Integrated Circuit.

**CPU** The Central Processing Unit (CPU) is a processor of a computer system.

CTS Clear To Send (CTS) is control signal where a receiver notifies the sender that they are ready to receive a data transfer.

**CUDA** Compute Unified Device Architecture (CUDA) is an application programming model developed by Nvidia for their GPUs.

**D2D** A term used to describe copying data from device memory to device memory.

**D2H** A term used to describe copying data from device memory to host memory.

DL Deep Learning is a subset of Machine Learning based on Artificial

Neural Networks with representation learning.

**DNN** A DNN is a Deep Neural Network with many layers between its inputs and outputs.

FIFO First-In First-Out (FIFO) is a method of processing data in a data structure such as a buffer. The first data item placed in the buffer is the first to be removed and processed.

**FPGA** An FPGA is a Field Programmable Gate Array.

Glossary xvii

**GPGPU** General Purpose Graphics Processing Unit is a piece of computer hardware designed for Data-Level Parallelism.

**GPU** See GPGPU.

H2D A term used to describe copying data from host memory to device memory.

HPC High-Performance Computing (HPC) is a large computer system used to solve complex problems.

**MP** In this thesis we may refer to our multi-path design as MP.

MPI The Message Passing Interface is a standardised and portable message passing standard for parallel programming.

NCCL The NVIDIA Collective Communication Library (NCCL) is a multi-GPU communication library for Nvidia GPUs.

NIC A Network Interface Card (NIC) is a piece of hardware that connects individual nodes to a network.

**NUMA** Non-Uniform Memory Access is a computer memory design used in multiprocessors.

**NVCC** Nvidia CUDA Compiler is a proprietary compiler by Nvidia which is used to compile CUDA programs.

**NVLink** NVLink is a wire-based communications protocol for intra-node communication developed by Nvidia.

**NVVP** The Nvidia Visual Profiler is a performance profiler for Nvidia CUDA code.

PCIe PCIe (Peripheral Component Interconnect Express) is a high-speed serial bus standard for connecting high-speed components such as GPUs and network cards.

RTS Request To Send (RTS) is control message where a sender asks to the receiver if they can transfer data.

Glossary xviii

$\begin{tabular}{ll} \bf UCX & Unified Communication X (UCX) is an open-source communication \\ framework for high-performance applications. \\ \end{tabular}$

# Chapter 1

# Introduction

High-Performance Computing (HPC) often refers to using the aggregate compute power of many small compute nodes to solve large complex problems. This allows us to solve problems that would take months or years on commodity workstations. HPC systems are usually used for solving scientific and engineering problems within many domains. Recent improvements in HPC technology has resulted in advances in Artificial Intelligence (AI), Machine Learning, and Deep Learning (DL). Deep Neural Networks (DNNs) have been used to provide solutions to many problems within natural language processing, image recognition, autonomous vehicles, cancer detection, and medical imaging, to name a few. Training of these DNNs are usually limited by hardware resources which result in long training times and low productivity from researchers. As the size of data sets and the complexity of DNNs grow, the requirement for computing resources continues to increase. Scaling of these DL applications to massively parallel systems is required to continue solving problems in this domain.

Both HPC and Deep Learning applications place a large amount of pressure on the communication subsystem of HPC clusters. Their performance is significantly affected by the underlying hardware and software. Simultaneously, the prevalence of accelerators has developed a need for system software to adapt to these changes. General Purpose Graphics Processing Units (GPGPUs) are one of the most popular accelerators used today. We often see multi-GPU computing nodes with their own proprietary intra-node interconnects to accommodate communication between GPUs.

Developing applications on HPC systems relies on programming models designed for these systems. The Message Passing Interface (MPI) [1] is one of the most popular programming models used today with multiple implementations such as MPICH [2], MVAPICH2 [3], and Open MPI [4]. On GPU-based HPC clusters it is beneficial for MPI to be GPU-Aware and allow for optimised communication between GPU memory regions. MPI supports point-to-point, collective, and remote memory access (RMA) communication operations. MPI collectives, in particular, MPI\_Allreduce and MPI\_Bcast, which involve communications among a group of processes, play a crucial role in the performance of MPI applications, including Deep Learning workloads.

## 1.1 Motivation

MPI is the *de facto* standard for parallel programming within HPC environments. The MPI standard defines many different API calls to transfer data between processes. These data transfers place a lot of pressure on HPC systems as they are more costly than transferring data within a single process. MPI communication performance has been a large problem for HPC applications [5,6]. Therefore, Investigating MPI communication challenges is incredibly important as it affects many problem domains.

With the growth of Deep Learning, many frameworks have been developed to scale existing applications to HPC clusters using MPI. There are many frameworks available for distributed Deep Learning such as TensorFlow [7], PyTorch [8],

Horovod [9], CNTK [10], and Deep500 [11]. Some frameworks, such as Horovod, implement distributed training using MPI but rely on other frameworks such as TensorFlow or PyTorch for the computation portion of their code. Other frameworks such as CNTK and Deep500 provide both distributed training tools and the implementation of Deep Learning models. As all these frameworks use MPI in some capacity, it is important to understand their usage. Some existing work shows that these applications use collective communication extensively [12–14] especially with large GPU messages. The exact usage of MPI collectives themselves is unclear and whether these applications use collective communication exclusively or a mixture of point-to-point and collectives. Gaining deep insight into the MPI communication characteristics such as the frequency of collectives or point-to-point, message sizes, or data volume, for a variety of DL frameworks, models, and optimisation algorithms will give us a clearer view of MPI-based Deep Learning.

Whether an application uses point-to-point or collective communication, improving point-to-point communication should improve most applications as collectives are often implemented upon point-to-point. The exact relationship between point-to-point communication and collectives differ between MPI implementations. Improving point-to-point communication for large messages can be achieved by fully utilising the available bandwidth. A higher bandwidth allows for data to be transferred in less time. As these Deep Learning applications are GPU-Centric it is important to investigate methods in which we can improve the available bandwidth for GPU-to-GPU data transfers.

## 1.2 Research Objectives

In this work we plan to investigate MPI based Deep Learning frameworks and GPU MPI communication. We aim to develop a better understanding of a few Deep Learning frameworks within the context of MPI and the communication character-

istics that are present during their execution. Our goal is to study both CPU and GPU-based Deep Learning frameworks to identify their differences and similarities. As our main interest is in GPU-based Deep Learning, we also investigated GPU communication on Nvidia's intra-node interconnect NVLink [15]. Finally we try to draw a connection between the communication characteristics and GPU communication. In this work we aim to answer the following questions:

- Is MPI communication a major bottleneck to Deep Learning applications? Are there similar MPI communication problems across different applications or does each application have unique characteristics? Do we face communication challenges with data residing in GPU or CPU buffers? Does Deep Learning depend upon MPI point-to-point or collective communication, or both? Which MPI communication calls are called more frequently and which are the most important in regards to improving application run-time?

- Is intra-node communication important for Deep Learning applications? If so, can we improve GPU point-to-point communication within a single compute node? Could our improvements in MPI point-to-point communication help accelerate MPI collectives too?

- If MPI point-to-point or collective communication is problematic in distributed training of Deep Learning models, can we design communication mechanisms that have a direct impact on these applications?

### 1.3 Contributions

In this thesis we make a few observation with regards to Deep Learning frameworks and a few proposals for the MPI communication run-time. MPI communication is critical for distributed Deep Learning frameworks. Improving the MPI communication run-time should yield major performance improvements. We contribute by providing an improved point-to-point communication mechanism to better utilise

bandwidth. We then use this mechanism to improve the MPI\_Allreduce collective communication performance. Finally we see these MPI communication run-time improvements impact the application layer by accelerating Deep Learning workloads [16].

- We observe that MPI\_Allreduce is the most prominent collective used by Horovod + TensorFlow, Horovod + PyTorch, and CNTK. For the CPU version Horovod + PyTorch, MPI\_Allreduce takes up to 90% of application run-time at 512 processes. For both GPU configurations of Horovod, MPI\_Allreduce takes up to 73% of application run-time at 64 GPUs. The message sizes used by both Horovod GPU configurations, resulted in mostly small CPU messages (less than 32B) and large GPU messages around 64MB. We observed that point-to-point communication was only used by CNTK and that point-to-point communication did not generate any message queue problems.

- We propose a novel multi-path GPU-to-GPU data transfer mechanism that partitions large point-to-point messages across device-to-device and device-to-host/host-to-device channels to utilise all available NVLink paths using a UCX one-sided put operation. Our approach achieves 1.69x and 1.84x higher bandwidth for UCX and Open MPI + UCX, respectively.

- We propose a 3-stage hierarchical, pipelined MPI\_Allreduce collective design that utilises the new multi-path copy mechanism for intra-socket data transfers, while dynamically selecting NVLink and PCIe channels for different stages of the algorithm to minimise interference. Our experimental results show a speedup of up to 12.25x, 15.63x, 3.72x, 1.48x, and 1.38x against Spectrum MPI, Open MPI + UCX, Open MPI + HPC-X, MVAPICH2-GDR, and NCCL, respectively.

- We evaluate the impact of the proposed multi-path copy and MPI\_Allreduce design at the application layer. For Horovod with TensorFlow training VGG16,

we observe up to 2.98x, 3.42x, 3.22x, 1.23x, and 3.24x speedup over Spectrum MPI, Open MPI + UCX, Open MPI + HPC-X, MVAPICH2-GDR, and NCCL, respectively. For ResNet50, we achieve 1.50x, 1.57x, 1.22x, 1.24x, 1.23x speedup over these MPI libraries, respectively.

# 1.4 Outline

The rest of this thesis is structured as follows: in Chapter 2, we introduce HPC clusters, MPI in greater detail, GPUs and Deep Learning. In Chapter 3 we analyse a few Deep Learning frameworks and observe their MPI communication characteristics. Then in Chapter 4, we propose a new multi-path UCX Put operation which better utilises NVLinks and we observe its impact on the MPI communication run-time. We then use this multi-path copy in MPI\_Allreduce in Chapter 5, and evaluate it against Horovod + TensorFlow while studying a few different Deep Learning models. Finally we make our concluding remarks in Chapter 6.

# Chapter 2

# Background

Parallel computing is a form of computation where a problem is split into smaller parts which can be solved in parallel. Parallel computing is often applied to compute clusters as they are many small systems connected together with some form of network. Traditional compute clusters are homogeneous and are CPU based. Heterogeneous computing is growing evermore important in cluster computing as we move away from homogeneous systems towards those with accelerators. As of 2021, many forms of accelerators are being researched such as AI ASICs, FPGAs and GPGPUs. GPGPUs have been one of the most popular accelerators for HPC systems. From the list of the Top500 supercomputers, 6 out of the top 10 are GPU based systems [17]. Accelerators allow users to offload highly parallel and compute intensive portions of their applications using vectorised operations. Accelerator offloading usually outperform using the CPU alone. With these new GPU systems being available to researchers, applications are also moving in a direction to utilise accelerators. HPC applications have been modified to utilise these compute resources such as HOOMD-blue [18], LAMMPS [19], and many more. As discussed in [20] we saw the growth of GPU-Centric Deep Learning with [21,22] as they were one of the first to start utilising their compute power in this domain.

In this section we provide background knowledge of HPC clusters, GPUs in this context and GPU-Aware MPI point-to-point and collective communication. Then we introduce parallel and distributed Deep Learning and their relation to the these HPC technologies.

# 2.1 Modern Heterogeneous HPC Clusters

A HPC cluster often contains a large number of nodes (individual computers) that are connected together to aggregate the compute power of the individual nodes. Having an aggregate of the compute power allows users to solve large complex problems which cannot be solved by a single machine in a reasonable time. In homogeneous systems, generally we have many CPU nodes of the same type. The individual CPU nodes can consist of one or more CPUs. Heterogeneous clusters are usually the same as homogeneous clusters but with the addition of hardware components such as accelerators. Hardware accelerators appear in many forms but their main purpose is to perform certain computations more efficiently than what can be computed on a CPU. Accelerators usually have certain compute operations implemented in hardware which often outperform general-purpose units. This usually decreases run-time and increases throughput of these operations. When working with systems with accelerators many challenges occur during software developments as we now need to account for communication time to transfer data to these accelerators.

Currently the most popular accelerator used in heterogeneous HPC systems are GPGPUs. GPUs were initially designed for hardware acceleration of computer graphics tasks. As GPUs are highly parallel, they eventually found their way into scientific computing. GPUs are connected to CPUs via various interconnects such as Peripheral Component Interconnect express (PCIe) or Nvidia's NVLink [15]. The intra-node interconnect topology can vary from system to system. Whether the system is homogeneous or heterogeneous, usually one or more Network Interface Cards

Figure 2.1: Schematic diagram of a modern heterogeneous HPC cluster

(NICs) are present to connect the nodes together using a switched network or fabric. Many network solutions exist such as Cray Aries Network [23], Intel Omni-Path Architecture [24], and InfiniBand [25].

In Figure 2.1 we can see a schematic diagram of a modern heterogeneous HPC cluster. The nodes are connected together in a fat tree topology where each node is connected to a switch. Then a second switch connects the first layer switches together. The second layer switches have higher bandwidth connections than the first. The nodes themselves contain a mixture of CPUs, GPUs, and NICs. The exact arrangement of the network switches and the intra-node topologies vary with each compute cluster.

# 2.2 Graphics Processing Units (GPUs)

GPUs are often found in the form of hardware accelerators in HPC systems. They are used to offload computation that would often be computationally intensive on CPUs. Within HPC, GPUs are generally used for floating-point operations computing matrices and vectors. There are many GPU vendors such as Nvidia, AMD, and Intel. The research conducted in this thesis is not bound to Nvidia GPUs but the work presented in this thesis will focus on Nvidia's V100 GPUs.

#### 2.2.1 GPU Architecture

The V100 GPU is comprised of 84 Streaming Multiprocessors (SMs) [26]. SMs are the part of the GPU which execute CUDA kernels, but their design is significantly different than other hardware like CPUs. These GPUs also have a memory hierarchy; registers allocated to threads inside the SM, local memory to hold thread variables, shared memory for threads within a block to communicate, and finally global memory which is accessible by all SMs. The global memory in the V100 GPUs is High Bandwidth Memory 2 (HBM2). The send and receive buffers used in MPI will be allocated within global memory. We will discuss MPI further in Section 2.4.

#### 2.2.2 Programming Nvidia GPUs

CUDA is a general-purpose parallel programming model that allows users to take advantage of Nvidia GPU's parallel compute engines. The CUDA environment allows users to program in C++ but CUDA can be interfaced with other languages such as C or FORTRAN. CUDA helps solve some of the challenges with transparently scaling applications in parallel environments. One of the main components of CUDA programming are kernels. These are similar to traditional functions in C/C++ but they can be executed in parallel using many CUDA threads. Each CUDA thread executes a kernel using its own thread ID.

#### **Streams**

CUDA applications concurrently transfer data and execute kernel via the concept of streams. A stream can be thought as a First-In First-Out (FIFO) queue of operations that will be executed in the order they are placed in the queue. Streams are in order with respect to themselves but work that is placed on multiple streams will not be in order relative to each other. Each stream will execute their commands

concurrently. Streams can be synchronised individually or all streams on a single device can be synchronised.

#### **CUDA** Events

Nvidia devices can asynchronously record events. Recording of events are placed on streams. Once the stream reaches a record operation in the execution sequence, it will modify an event object. These event can also be queried to synchronise work between distinct streams.

#### CUDA Inter-Process Communication (IPC)

Device pointers are bound to the context that it was created in. Therefore, these pointers cannot be passed between processes via the usual means such as message passing or shared memory. To share device pointers and CUDA events between processes, the CUDA IPC API must be used [27]. Using the IPC API we can create a handle for a device pointer or an event and pass that handle to another process. That other process can open the handle to obtain a device pointer or event which can be used within that context.

## 2.3 Network Interconnects

GPU compute nodes usually have an interconnect to interface the multiple GPUs together within a single node. For the work presented in this thesis, we have worked with systems that use PCIe and/or NVLink. For HPC clusters, there is usually an interconnect to connect the individual nodes together. Many network solutions exist such as Cray Aries Network, Intel Omni Path Architecture, and InfiniBand. For the work in Chapter 3, we use an InfiniBand network.

#### 2.3.1 PCIe

PCIe [28] is a high-speed interconnect used in compute systems to connect devices to CPUs. Many devices can be connected to the CPU with this interconnect such as GPUs, NICs, and SSDs. There are a few physical configurations for PCIe slots such as x1, x4, x8, and x16. Each configuration provides a different number of PCIe lanes to the attached device. An increase in lane count results in an increase in the available bandwidth to the device. GPUs attached via PCIe are often attached with x16 slots. For a PCIe 3.0 x16 slot, we would have a bi-directional bandwidth of 32GB/s and for PCIe 4.0 x16 slot we would have 64GB/s.

#### 2.3.2 NVLink

NVLink [15] provides connectivity between Nvidia GPUs on multi-GPU systems. The main advantage of NVLink over PCIe for Nvidia GPUs is the increased bandwidth available for data transfers. The V100 GPUs discussed in this thesis has 6 attached NVLinks providing a total bi-directional bandwidth of 300GB/s (50GB/s per link). Depending on the system, the NVLinks are arranged in multiple different topologies. These topologies will be discussed in Chapter 4 when we introduce the compute systems that we will work with.

#### 2.3.3 InfiniBand

InfiniBand (IB) [25] is a network specification maintained by the InfiniBand Trade Association. IB is used to connect high-performance compute node together which provides high throughput and low latency. The IB network used in the this thesis is Nvidia Mellanox EDR InfiniBand interconnect which provides 100Gb/s of bandwidth.

# 2.4 The Message Passing Interface (MPI)

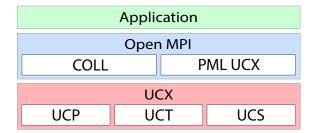

The Message Passing Interface [1] is one of the most dominant programming models within HPC. MPI allows for the transfer of data between distinct processes. One of the main benefits of using MPI over other alternatives, such as the NVIDIA Collective Communication Library (NCCL) [29], is MPI's scalability, ability to use buffers from different memory regions, and portability. In Figure 2.2 we can see MPI's relation to other software libraries in a Deep Learning software stack.

MPI has three modes of communication; point-to-point, one-sided, and collectives. When using point-to-point communication, two processes are active with one sending data to another who is receiving. These send/recv pairs are matched. MPI guarantees that every message will arrive in order with no errors from the applications perspective. With one-sided communication, the data movement is decoupled from process synchronisation. One process exposes a memory region and another can read/write from that location. Only one process is active during the data trans-

Figure 2.2: Software Stack

fer. Collective communication allows for data to be transferred between multiple process in a predefined pattern between processes.

#### 2.4.1 Point-To-Point Communication

Point-to-point communication involves two processes which directly transfer data between them. One process issues a send call and the other issues a receive call. The sent message contains two parts, the envelope and the data itself. The message envelope contains data about the message being sent such as the rank, tag and communicator. MPI provides both blocking (MPI\_Send and MPI\_Recv) and non-blocking (MPI\_Isend and MPI\_Irecv) routines for point-to-point communication.

Most MPI implementations have two protocols for sending messages, *Eager* and *Rendezvous*. Generally the Eager protocol is used for small messages and Rendezvous is used for large messages.

Eager: With the Eager protocol, the sender assumes that the destination process has sufficient allocated to store the incoming message. Therefore the sending process transfers all of the data to the receiver directly.

Rendezvous: With the Rendezvous protocol, the sender assumes that the destination process may not have allocated memory to store the incoming message. As we do not have the guarantee that there is allocated memory, the protocol executes a handshake to ensure that the data can be sent. The sender sends a Request To Send (RTS) control message to the receiver. Once the receiver has allocated memory to receive a message, it notifies the sender with a Clear To Send (CTS) control signal. Now the sender process transfers the data into the buffer of the receiver process.

#### MPI Message Queues

MPI implementations usually have two message queues to handle communication when two processes are out of sync. The two message queues are the Unexpected Message Queue (UMQ) and the Posted Receive Queue (PRQ). When MPI\_Recv is

called, the process first checks the UMQ to see if a message has arrived before MPI\_Recv was called. If so, the message is removed from the UMQ. In the other scenario where MPI\_Recv is called and the UMQ does not contain the message that the process is looking for, then the receive call is placed on the PRQ. Once the message arrives from the network, PRQ is checked for a matching receive call. If so, the receive call is removed from the PRQ and then the data transfer is complete. When searching for a message on the queue, a comparison is made with the message envelope that is created by the MPI\_Recv call. Although this was described using blocking point-to-point calls the same is true for non-blocking calls.

#### 2.4.2 Collective Communication

Collective communication occurs between a group of processes. This group is defined by an MPI\_Comm object which is a communicator. The communicator MPI\_COMM\_WORLD refers to all processes that are present when a parallel job starts. Collective communication can be placed into four different categories; All-To-All, All-To-One, One-To-All, and Other [1,30]. Three of the categories can be seen in Figure 2.3. Within the All-To-All category all processes contribute to the result and all processes receive the result. This pattern can be seen in MPI\_Allreduce, MPI\_Alltoall, and

Figure 2.3: Different MPI Collective Communication Patterns

MPI\_Allgather. All-To-One is where all processes contribute to the result and one process receives the result. MPI\_Reduce and MPI\_Gather are examples of this. In One-To-All communication, one process contributes to the result and all processes receive the result. MPI\_Bcast and MPI\_Scatter use this the pattern. MPI calls such as MPI\_Scan and MPI\_Exscan do not fit into the three previously discussed categories and are placed in the 'Other' category. For example, with MPI\_Scan,  $P_0$  receives it data from a single process but  $P_n$  receives its data from all n processes. Therefore, the communication pattern is different for each process in the communicator and does not fit in these three categories. For collectives such as MPI\_Allreduce, MPI\_Reduce\_scatter, and MPI\_Scan, there is a computation that also occurs along the communication within the collective. This computation can be defined by the MPI\_Op parameter.

#### $MPI\_Allreduce algorithms$

This thesis will focus on the MPI\_Allreduce collective as it is extensively used in Deep Learning and is a major performance issue for many frameworks. The performance issues will be discussed further in Chapter 3. Many different MPI\_Allreduce algorithms exists, where they each optimise different metrics such as bandwidth or latency. Each algorithm performs differently based on process count, message sizes, and the system. We discuss the four algorithms implemented in Open MPI [4]: Linear, Ring, Recursive Doubling, and Reduce-Scatter Allgather (RSA). The Ring and Segmented Ring algorithms will be discussed together as the difference between the two is small. Diagrams in this section are shown for four processes, as that is what we use in Chapter 5 but these algorithms work for any process count.

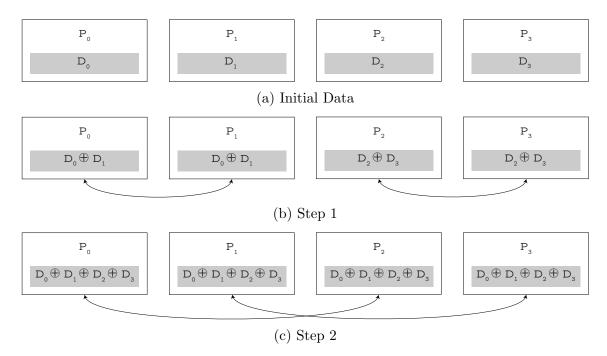

Reduce-Broadcast (Linear): This algorithm is one of the simplest implementations of MPI\_Allreduce. It shows the fundamental behaviour of the algorithm in an easy manner. All processes directly send their data to the root process. In Figure

Figure 2.4: MPI\_Allreduce Reduce-Broadcast algorithm for 4 processes

2.4 we show the root process as  $P_0$ . Once all the data has been received at the root, the process reduces the data. This reduction can be MPI\_SUM, MPI\_MAX or many other MPI\_Op parameters. In the diagram the reduce operation is denoted as  $\oplus$ . Once the data has been reduced, the root process then sends a copy of the reduced data to all other processes in the communicator. The root process also copies the reduced data into its own receive buffer.

Recursive Doubling (RD): Figure 2.5 illustrates recursive doubling for four processes. In the first step processes exchange data with ranks that have a distance of one. Once each process has a copy of its partner processes data, it reduces the data. Then in Step 2, each process exchanges its data with ranks that have a distance of two. Again this received data is reduced. For four processes, this is the last step so data is then copied to the receive buffer. This algorithm can be generalised for any process count. Recursive doubling is often used for smaller message sizes.

Figure 2.5: MPI\_Allreduce Recursive Doubling algorithm for 4 processes

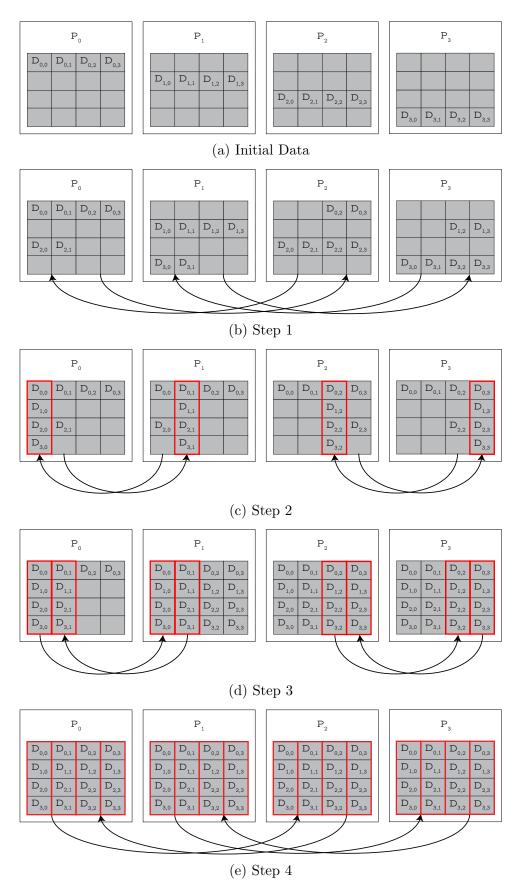

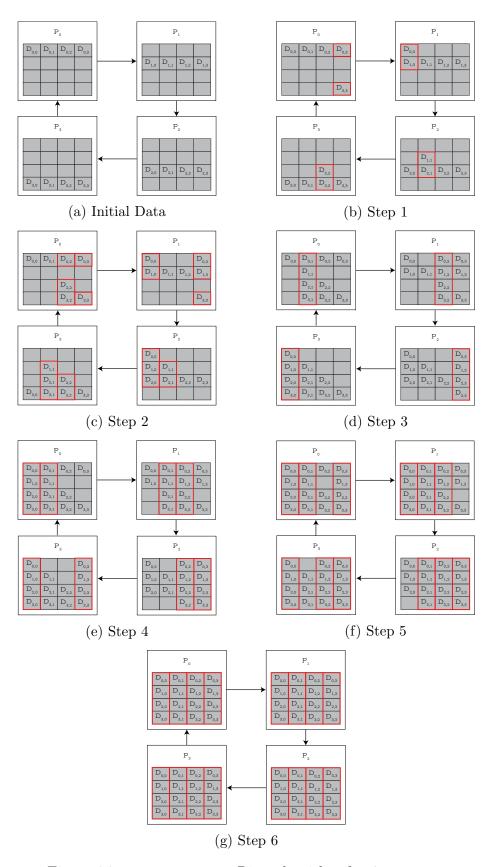

Reduce-Scatter Allgather (RSA): has two main parts as per its name. In Figure 2.6 we can see that Steps 1 and 2 act as Reduce-Scatter and Steps 3 and 4 act as Allgather. For the description of this algorithm we have not shown it with the  $\oplus$  operator as this algorithm also divides the buffer during its execution. The red boxes denote that the data has been reduced. Here we denote the data  $D_{rank,chunk}$  where each rank has four chunks. This algorithm can be generalised for n ranks which will result in n chunks. In Step 1 we send half of the buffer to processes with a distance of two. In Step 2 we send one quarter of the buffer to processes with a distance of one. Then we reduce the data. For each step the data size is halved. We can see from Figure 2.6 that the buffer chunks are chosen so that by the end of Step 2 we have executed a reduce-scatter. Now to complete the algorithm, we must execute Allgather to distribute the reduced data across the processes. In Step 3 we exchange the reduced data with processes with a distance of one. Then the reduced data is exchanged with processes with a distance of two. Now each process has a copy of the reduced data.

Figure 2.6: MPI\_Allreduce RSA algorithm for 4 processes

Figure 2.7: MPI\_Allreduce Ring algorithm for 4 processes

Ring: Here we will discuss both the ring and segmented ring algorithm as they are fairly similar with small differences. In Figure 2.7 it can be seen that the processes are organised in a ring topology where each process sends to only one other process and receives from a single process. With the ring algorithm, the buffer is split into N chunks. For the default ring implementation in Open MPI, N = P where P is the number of ranks. Steps 1-3 act as a ring-based reduce-scatter and Steps 4-6 act as an allgather. In Figure 2.7 we see the default ring implementation where N=P. So here the buffer is split into 4 chunks. At each algorithm step one chunk is sent to the next process. In Step 1 the first chunk is sent. In Step 2 the original data chunk is reduced with the chunk of data which was received in Step 1 and sent on to the next process. Step 3 is a repetition of Step 2 but as the rank now has all of the data the buffer is fully reduced for one chunk. This is shown with the red box. At the end of Step 3 the reduce-scatter is complete as each process has one quarter of the buffer that is fully reduced. In Step 4 the reduced data is sent to the adjacent rank. This is also repeated for Step 5 and Step 6 until every process has a fully reduced buffer.

In this example there are a total of 6 steps. This can be generalised for P processes. The first reduce scatter step takes (P-1) steps, then the allgather step also takes (P-1) steps. Therefore the ring algorithm has a total of 2(P-1) steps.

#### 2.4.3 GPU-Aware MPI

When an MPI implementation is GPU-Aware it usually refers to being able to pass pointers into the send/recv buffer of GPU memory regions. The MPI implementation handles the explicit data transfer between GPU and the Host.

# 2.4.4 MPI Implementations

The Message Passing Interface is a standard which is approved by MPI Forum [1]. There are many implementations which follow this standard, some implementations are generic such as MPICH [2] and Open MPI [4] but others are are designed for specific hardware architectures such as Cray-MPICH [31] or Spectrum MPI [32]. In this thesis, the following implementations were used MVAPICH2, MVAPICH2-GDR [3], Spectrum MPI [32], Open MPI [4], and Open MPI + HPC-X [33].

#### **MVAPICH2**

MVAPICH2 is an MPI-3.1 implementation based on MPICH. MVAPICH2 is an open source implementation provided by The Network Based Computing Laboratory (NBCL) at The Ohio State University (OSU). MVAPICH2-GDR is a closed source implementation which is highly optimised for GPU-based workloads. MVAPICH2 was used in Chapter 3 for the Deep Learning characterisation work. MVAPICH2-GDR was used in both Chapter 4 and Chapter 5 to compare results with the proposed work in that chapter.

### Open MPI + UCX

Open MPI is another open source implementation of MPI. It was used in both Chapter 4 and Chapter 5. Unified Communication X (UCX) was used for Open MPI's Point-to-point Management Layer (PML) component. Open MPI can use other point-to-point components in the PML, such as ob1, but better performance was observed when using UCX on the compute systems used in Chapter 4 and Chapter 5. Open MPI uses UCX's point-to-point features for its own point-to-point and collective implementation. When using point-to-point communication in MPI, we are directly using the point-to-point communication interface of UCX. For collective communication, UCX is abstracted through the PML layer, as shown in Figure 2.8. Figure 2.8 provides a slightly more detailed view of Open MPI + UCX than what was presented in Figure 2.2. Open MPI supports various flat algorithms for MPI\_Allreduce, where the algorithm is chosen at run-time based on

Figure 2.8: Simplified Software Stack of Open MPI + UCX

the number of processes and the message size. Flat algorithms are designed in a non-hierarchical approach and executed across all process in the cluster. In a flat algorithm, any pair of processes can communicate at the same cost. The following algorithms are implemented within Open MPI; ring, segmented ring, reduce-scatter-allgather, recursive doubling, nonoverlapping, and linear. Open MPI provides GPU support but for collectives with data residing on the GPUs it copies the data to the host and uses CPU based operations. Open MPI is not well optimised for GPU workloads.

Nvidia provides an additional component for Open MPI called HCOLL which is included in their HPC-X package. This component provides accelerated collective communication for Open MPI. For point-to-point communication, this component still depends on UCX. We have called this package Open MPI + HPC-X throughout this thesis.

Unified Communication X (UCX): UCX is an RDMA-based point-to-point communication library for modern low latency, high bandwidth interconnects [34]. It provides an abstract interface for communication that allows for network acceleration across many interconnects. In Figure 2.8, we see a simplified diagram of UCX relevant to this thesis.

Unified Communication Protocol (UCP) Layer: The UCP layer of UCX implements high level protocols that are used by other communication libraries such as MPI. UCP supports Remote Memory Access (RMA), active messages, and tag-

matching operations, among others. The tag-matching interface is the most relevant to our work as it supports tag-matching for send-recv semantics of MPI. For this interface, UCP implements both the *Eager* and *Rendezvous* protocols. The UCP layer uses the UCT layer to implement these different protocols over a wide range of transports.

Unified Communication Transport (UCT) Layer: The UCT layer is a transport layer that abstracts the data movement across different memory regions. This layer uses low-level driver APIs such as InfiniBand Verbs, libfabrics, GDRCopy, and CUDA IPC to allow for efficient access to hardware with minimal overhead. This layer defines interfaces for small messages (short), buffered copy-and-send (bcopy), and zero-copy (zcopy) operations. In Chapter 3, it was shown that large GPU messages are important for Deep Learning workloads. Therefore, the zcopy operation for the CUDA IPC component of the UCT layer is important as this is where large GPU messages are transferred. This component handles GPU-to-GPU communication semantics via the usage of CUDA IPC. First, the receiver process places the CUDA IPC memory handle into shared memory. Then, the sender opens the handle and uses a Put operation to place the data into the remote process.

# 2.5 Distributed Deep Learning

Deep Learning is a subset of Machine Learning which often learns representations of data using Artificial Neural Networks (ANN). Deep Learning uses Deep Neural Networks (DNN) which is an ANN with many layers between its inputs and outputs. DNNs usually use convolution operations throughout a model architecture for many different models.

# 2.5.1 Distributed Training

There are two main methods of distributed training; data parallelism and model parallelism. At the time of writing this thesis, data parallelism seems to be the more

popular method as its ecosystem is more mature. Model parallelism still appears to be in the research stage of development [35,36].

#### Data Parallelism

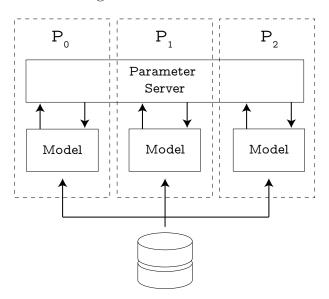

Training using the data parallel method involves having multiple processes, where each process has an instance of the Deep Learning model. Here the data set is split between the different processes and each process trains independently on that subset of data. This is useful for scenarios where the batch size cannot fit into GPU memory so that batch is split among processes. After a process trains its model, it must average the model parameters across all the processes to create a consistent global model. Usually a parameter server average the gradients across the different processes. If a single parameter server is used on rank 0, then all processes send their gradient to rank 0, and then average is calculated. Finally the average is broadcasted to all other processes. A parameter server can be centralised and have a single instance, as per the previous example, or it can be implemented in a decentralised manner where it is distributed across the processes. A decentralised parameter server is shown in Figure 2.9.

Figure 2.9: Schematic diagram of distributed training using data parallelism

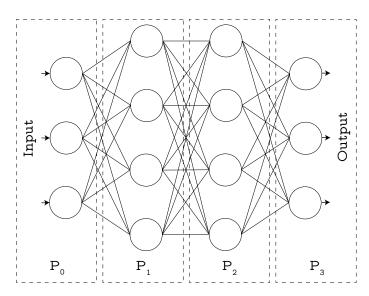

#### Model Parallelism

Model Parallelism is where the Deep Learning model itself is parallelised. In Figure 2.10 we see that a model can be split among processes. Each process performs a part of the computation. This is usually used when a single model cannot fit into GPU memory or to create pipelining with computationally intensive layers. As Model Parallelism is not used in this thesis, this section is brief.

# 2.5.2 Deep Learning Frameworks

Programming Deep Learning models using language primitives is often a complex task. To simplify this process, many frameworks exist to provide high-level APIs containing the basic operations used in Deep Learning. In this thesis we will look at four popular frameworks: TensorFlow [7], PyTorch [8], Horovod [9], and CNTK [10]. These frameworks are built in mostly C/C++ and Python and they also provide their high-level APIs in those languages. CNTK also provides API in binding BrainScript.

Figure 2.10: Schematic diagram displaying an example of model parallelism using 4 processes

#### TensorFlow

TensorFlow is an open source Machine Learning framework, supported by Google, which allows for using symbolic math operations for data-flow and differentiable programming [7]. TensorFlow provides tools to deploy Machine Learning models in the web browser, mobile and IOT devices, and in production environments such as data centres. Although there was some work into using distributed TensorFlow using MPI [37], as of TensorFlow version 2.0, it no longer uses MPI for distributed training. For our work we are predominately interested in its implementation of GPU accelerated Deep Learning models, such as ResNet-50, which will be used with Horovod.

#### **PyTorch**

PyTorch is a an open source Machine Learning framework which is built upon Caffe [38] and developed by FaceBook AI Research Lab (FAIR) [8]. PyTorch allows for multiple communication backends for distributed training such as: NCCL, MPI, and GLOO. It is also possible to train PyTorch models using a single process.

#### Horovod

Models built using TensorFlow and PyTorch can be trained in a distributed fashion using Horovod [9]. Horovod does not have the tools to build the models themselves and relies on third party libraries. Horovod uses the *data parallel* approach to scaling DL models. The data set is split across multiple GPUs and are processed independently. Then an allreduce algorithm is used to average the gradient and distribute the results [9]. This allreduce can be from NCCL, MPI, or a mixture of both libraries.

Horovod has a feature called *Tensor Fusion* which enables the overlap of communication and computation by batching data for MPI\_Allreduce operations. Tensor

Fusion first determines which tensors are ready to be reduced. Then it allocates the fusion buffer, whose size is determined by the run-time parameter HOROVOD\_FUSION\_TH-REASHOLD. The default size of the buffer is 64MB. Finally, the buffer is populated with the selected tensors and the reduction is executed. These steps are repeated until all tensors have been reduced.

#### **CNTK**

The Microsoft Cognitive Toolkit (CNTK) is an open-source distributed Deep Learning toolkit [10]. This toolkit is commercial grade. CNTK allows users to create many different models such as DNNs, CNNs, etc. Alongside the models, CNTK also implements a distributed Stochastic Gradient Descent (SGD) which is an iterative method for optimising an objective functions used in distributed training. CNTK uses MPI for its distributed training. CNTK is flexible in that it allows users to program an application in multiple different languages: Python, C#, C++ or Brain-Script. As of 2019, CNTK has been deprecated. It was included in this thesis as the work had been completed before the deprecation. That said, studying it still has its own merit from a research perspective as it is important to study many different Deep Learning applications.

# Chapter 3

# Communication Characterisation of Distributed Deep Learning Frameworks

In recent years there has been an increase in the popularity of Deep Learning applications, both to solve tradition problems in HPC and in new areas. However, the behaviour of these applications still have some degree of unknown characteristics from a system software perspective. In this chapter, we study the characteristics of distributed Deep Learning frameworks to find opportunities for optimisation.

As discussed in Chapter 2, distributed Deep Learning using MPI is an effective method to train these applications at scale. MPI usage can vary greatly from application to application. The behaviour of the MPI run-time is very dependent on which API calls are made. Depending on which portion of the library that an application uses, largely dictates which research areas could improve their performance. In this chapter, we characterise a few Deep Learning applications using the PMPI profiling interface of MPI. Application level profiling will allow for various metrics to be gathered such as frequency, time, and message sizes used by each API call.

Such metrics can guide research into the MPI run-time by determining potential performance problems. In this chapter we make the following contributions:

- We profiled two popular distributed Deep Learning frameworks, Horovod and CNTK. With Horovod we looked at using the framework with both Tensor-Flow and PyTorch for both CPU and GPU-based Deep Learning models. For CNTK, we investigated four different training algorithms.

- We measured the frequency of MPI point-to-point and collective communication calls made by both frameworks to determine which MPI API calls are of merit. From this, we measure the impact of MPI on application run-time for these calls. For the most used MPI calls, we collected and analysed the most frequently used message sizes.

- We also investigated a configuration of Horovod which uses a mixture of NCCL and MPI at run-time to see how NCCL can be used to offload MPI communication.

- For CNTK, we measured how long is spent in MPI message queues and its impact on application run-time.

# 3.1 Related Work

MPI communication characterisation has previously been studied in great depth for traditional HPC applications. A recent survey on US exascale computing projects showed that 73% of projects use MPI [39]. Application developers expect 89% of point-to-point communication and 93% collective communication to be performance critical for the exascale version of their applications. They also expect for applications to use multiple threads per process in 86% of their projects. A study on MPI usage on a production supercomputer showed that currently 30% of MPI jobs use multiple threads per process [40]. Although there is a large discrepancy in these values, it still shows that multi-threaded MPI is becoming more prominent.

MPI often contributes to large application performance bottlenecks as 15% of jobs spend over 80% of application run-time in MPI. Collective communication accounts for around 60% of total MPI time [40]. Five or fewer MPI calls account for 90% or more of the total communication calls for a particular application [6]. MPI\_Allreduce and MPI\_Bcast are the most frequently used collectives. MPI\_Allreduce, MPI\_Alltoall, and MPI\_Bcast transfer the largest volume of data. Applications which use collectives often send messages smaller than 2KB while those which use point-to-point often send larger messages [6]. Chunduri et al. found that 40% MPI jobs used messages less than 256B for reduction operations. In [41], most of the applications which they studied showed that smaller message sizes (<1KB) are more prominent. Each study shows slightly different results which suggests that this type of work is tightly coupled to the applications under test.

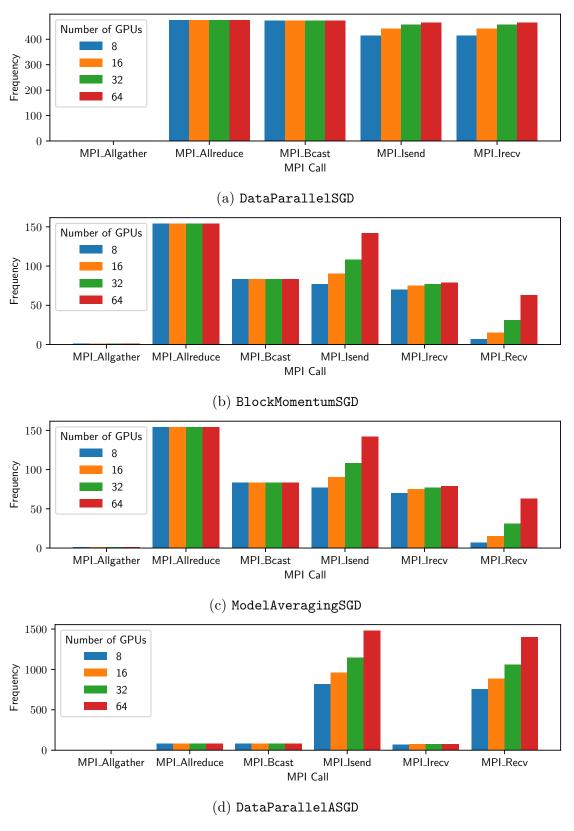

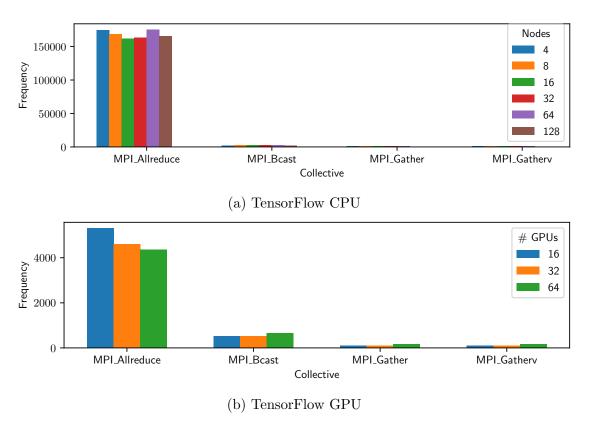

The communication pattern of point-to-point messages used by applications gives some insight into the network utilisation. Kamil et al. measured the topological degree of connectivity and found most applications have a low degree of connectivity and do not take advantage of the fully connected network that exists in many HPC systems [6]. Similar results were shown by Zamani and Afashi, and they also noted that some applications have a substantially higher frequency of sends/recvs to process 0 [41]. Frequent communication to a single process often results in applications developing long message queues [42].