# O-BAR: A Scalable, Optical Neuromorphic Communication Protocol

Mitchell A. Nahmias, Alexander N. Tait, Bhavin J. Shastri, and Paul R. Prucnal Lightwave Communications Laboratory, Department of Electrical Engineering, Princeton University, Princeton, NJ 08544, USA mnahmias@princeton.edu

Abstract—We propose an address event representation (AER) broadcast optical networking scheme to alleviate communication bottlenecks in electronic neuromorphic processors. This protocol is collision, router and switch-free, potentially supporting large ( $\approx 10,000$ ) neural fan-in and fan-out.

# I. Introduction

Spiking neural networks (SNNs) represent an alternative to the von Neumann paradigm of computation. They take advantage of distributed, sparse, and robust encoding schemes to perform computations with higher power efficiency and performance, and have been utilized both for biological network simulators and low-power data processors. Unlike interconnects in von Neumann processors, which are based on point-to-point communication between nodes, neural networks require many-to-one fan-in and significant multicasting, which can be a bottleneck in electronics.

Large-scale neuromorphic systems—such as IBM's TrueNorth architecture [1], SpiNNaker [2], and Brains on Silicon [3]—use packet switching, time division multiplexing (TDM), or crossbar arrays with complex routing protocols to side-step the electronic wiring bottleneck. Crossbar arrays can realize dense all-to-all interconnects, but are difficult to scale hierarchically to larger systems. In contrast, packet switching allows dense virtual interconnects, but at the cost of a communication and energy overhead.

Optical communication systems could provide an alternative, complementing the processing density of electronics with power-efficient, high bandwidth communication. Unlike electrical wires, optical signals consume less energy per bit, have a much larger bandwidth-distance product and a greater bandwidth-density per wire. The advantages are especially salient in a neuromorphic system, in which the primary system bottleneck is in communication rather than in processing. We propose O-BAR as an alternative to electronic packet switching: an Optical Broadcast Address event Representation network. The protocol is simple—free of collisions, routers, and switches—compatible with emerging trends in photonic integration, can support high-density interconnects, and can be scaled hierarchically to form large-scale neuromorphic systems.

# II. WORKING PRINCIPLES

Utilization of wavelength division multiplexing (WDM) is crucial in any parallelized interconnect fabric. Unfortunately,

the simplest approach—associating a single wavelength channel  $\lambda_i$  with each neuron—fails to utilize the full bandwidth of optics unless one operates at a faster time scale (as in [4]). Instead, we utilize a multiplexing scheme called address event represention (AER), in which a packet is release into the network containing only the identity of the neuron which has fired. This packet-based method allows multiple neurons to share a given wavelength channel to fully utilize available bandwidth.

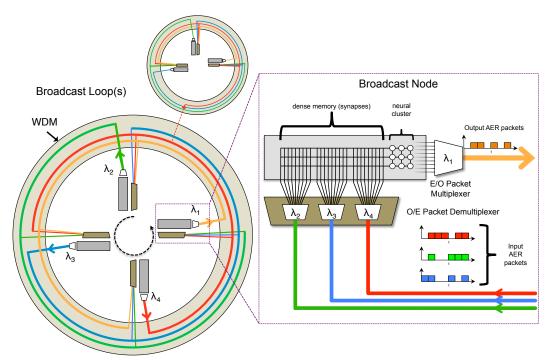

The architecture separates communication and processing into optical and electronic hardware, respectively, and has many topological similarities to the ORnOC architecture [5]. Communication centers around a WDM ring network as shown in Figure 1, which implements all-to-all WDM broadcasting. Each node contains a cluster of neurons and synapses in electronics for processing and programming, using AER protocols at the sender to multiplex asynchronous spikes and broadcast them to every other node. Each node receives simultaneous signals from all other nodes in the loop, which are demultiplexed and converted to electronic signals that interface with the neural cluster.

# A. Broadcast Node

Suppose there are N nodes, labeled from  $i=0,1,2\ldots N$ . Each broadcast node contains densely packed neurons and synapses and asymmetrically receives all wavelength channels C while outputting on only a subset of channels k=C/N. Clusters of n neurons (where n>k) share the channels k for outputs. Since neurons will release pulses asynchronously based on their input activity, the E/O Packet Multiplexer (as shown in Figure 1) must perform arbitrage and buffering to prevent multiple access collision. The arbitrage can be done locally at the sender, keeping the network collision-free. Meanwhile, signals from other nodes are demultiplexed and converted to electrical signals which are compatible with dense, locally-packed synapses to provide inputs to the neural cluster.

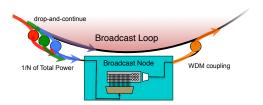

### B. Broadcast Loop

The broadcast loop is the medium through which all the AER packets are distributed to each node simultaneously, utilizing the extensive bandwidth of optics to perform high-throughput broadcasting. As Figure 2 shows, packets from a given cluster of neurons can coupled into the loop along a

Fig. 1. A schematic of the proposed architecture with four clusters of nine neurons each. Each cluster i functions locally. When a neuron fires, its identity is sent to the E/O packet multiplexer, which sends a unique orthogonal code (packet) along a given wavelength  $\lambda_i$ . Each  $\lambda_i$  channel is random access (i.e. neuron events are statistical multiplexed), but arbitrage is local to the sender so there are no network packet collisions. Balanced light-path splitting and filtering via drop-and-continue distributes the signal evenly to the other three clusters. The packets are demultiplexed and converted into electrical signals at the O/E packet demultiplexer, which modulating a densely clustered array of synaptic elements, driving the neural cluster. This miniature loop network alone supports 1296 synaptic connections. Multi-loop organization is possible through the sharing of channels or broadcast nodes across loops.

Fig. 2. Drop-and-continue allows a given node full access to the WDM broadcast space by dropping only a fraction of the total energy in the loop. Cross-waveguide filters also allow signals to be added without interference. High contrast waveguide technology (i.e. micro-rings, illustrated here) would allow for compact networks on chips (NoCs).

frequency (or set of frequencies k) via a WDM coupler. On the receiving end, drop-and-continue allows 1/N of the total power to be coupled into each node i while allowing the rest to continue, using carefully tuned filters.

The simplicity of this system originates from the large bandwidth of optical waveguides, which allow for a full superposition of all the signals onto a signal wire. With hundreds of neurons per channel and hundreds of channels—a feat achievable with today's technology—a fan-in of tens of thousands is possible without switches, routers, or packet collisions. The time bandwidth product puts the fundamental fan-in limit at approximately three billion for a given broadcast loop, which is far above any reasonable implementation requirements.

The scheme is flexible with regards to the underlying implementation, compatible with both Network on Chip (NoC) technologies and fiber networking. Advanced system-level

design—such as large-scale hierarchical organization—is also possible via multi-loop sharing of channels or broadcast nodes.

# III. CONCLUSION

We have proposed an optical networking protocol for event-based neuromorphic computing architectures that takes advantage of the massive bandwidth availability of optics to achieve all-to-all interconnection between neural clusters. This system compliments the dense processing and memory possible in electronics, and can support complex multi-loop topologies. This highly scalable platform could serve as the back-bone for future, large-scale neuromorphic systems.

#### REFERENCES

- [1] R. Preissl, T. M. Wong, P. Datta, M. Flickner, R. Singh, S. K. Esser, W. P. Risk, H. D. Simon, and D. S. Modha, "Compass: A scalable simulator for an architecture for cognitive computing," in *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis*, p. 54, IEEE Computer Society Press, 2012.

- [2] M. M. Khan, D. R. Lester, L. A. Plana, A. Rast, X. Jin, E. Painkras, and S. B. Furber, "Spinnaker: mapping neural networks onto a massively-parallel chip multiprocessor," in Neural Networks, 2008. IJCNN 2008. (IEEE World Congress on Computational Intelligence). IEEE International Joint Conference on, pp. 2849–2856, IEEE, 2008.

- [3] K. Boahen, "Neuromorphic microchips," Scientific American, vol. 292, no. 5, pp. 56–63, 2005.

- [4] M. A. Nahmias, A. N. Tait, B. J. Shastri, and P. R. Prucnal, "An evanescent hybrid silicon laser neuron," in *Proc. IEEE Photonics Conf.* (*IPC*), (Seattle, WA, USA), pp. 93–44, Sept. 2013.

- [5] S. Le Beux, J. Trajkovic, I. O'Connor, G. Nicolescu, G. Bois, and P. Paulin, "Optical ring network-on-chip (ornoc): Architecture and design methodology," in *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2011, pp. 1–6, IEEE, 2011.